# 200ball FBGA Specification

32Gb LPDDR4X (x32)

## **FEATURES**

## [LPDDR4X]

- VDD1 = 1.8V (1.7V to 1.95V)

- VDD2 = 1.1V (1.06V to 1.17V)

- VDDQ = 0.6V (0.57V to 0.65V)

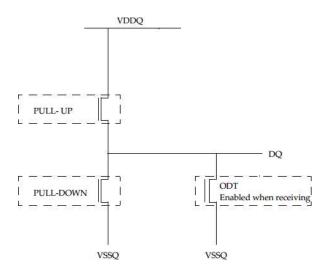

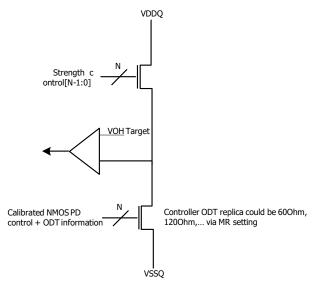

- Programmable CA ODT and DQ ODT with VSSQ termination

- VOH compensated output driver

- Single data rate command and address entry

- Double data rate architecture for data Bus;

- two data accesses per clock cycle

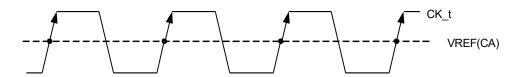

- Differential clock inputs (CK\_t, CK\_c)

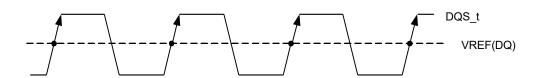

- Bi-directional differential data strobe (DQS\_t, DQS\_c)

- DMI pin support for write data masking and DBIdc functionality

- Programmable RL (Read Latency) and WL (Write Latency)

- Burst length: 16 (default), 32 and On-the-fly

- On the fly mode is enabled by MRS

- Auto refresh and self refresh supported

- All bank auto refresh and directed per bank auto refresh supported

- Auto TCSR (Temperature Compensated Self Refresh)

- PASR (Partial Array Self Refresh) by Bank Mask and Segment Mask

- Background ZQ Calibration

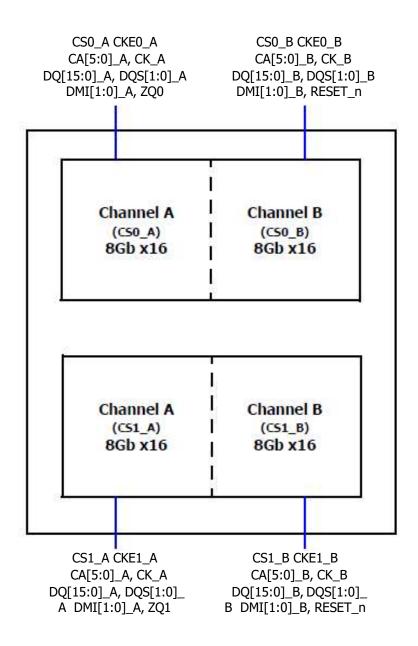

## **Functional Block Diagram**

REV 1.0 3 *DLI Memory, Inc.* 08/2023

# **ORDERING INFORMATION**

| Part Number       | Mode    | Operation Voltage | Density                  | Speed | Package                               | Operating<br>Temperature |

|-------------------|---------|-------------------|--------------------------|-------|---------------------------------------|--------------------------|

| DN4H32GCCPQI4-C2  | LPDDR4X | 1.8V/1.1/0.6      | 32Gb<br>(x16, 2 Channel) | 3200  | 200Ball FBGA<br>(Lead & Halogen Free) |                          |

| DN4H32GCCPQI4-C7  | LPDDR4X | 1.8V/1.1/0.6      | 32Gb<br>(x16, 2 Channel) | 3733  | 200Ball FBGA<br>(Lead & Halogen Free) | 0°C ~ 95°C               |

| DN4H32GCCPQI4-D2  | LPDDR4X | 1.8V/1.1/0.6      | 32Gb<br>(x16, 2 Channel) | 4266  | 200Ball FBGA<br>(Lead & Halogen Free) |                          |

|                   |         |                   | 32Gb<br>(x16, 2 Channel) |       | 200Ball FBGA<br>(Lead & Halogen Free) |                          |

| DN4H32GCCPQI4-C7I | LPDDR4X | 1.8V/1.1/0.6      | 32Gb<br>(x16, 2 Channel) | 3733  | 200Ball FBGA<br>(Lead & Halogen Free) | -40°C ~ 95°C             |

| DN4H32GCCPQI4-D2I | LPDDR4X | 1.8V/1.1/0.6      | 32Gb<br>(x16, 2 Channel) | 4266  | 200Ball FBGA<br>(Lead & Halogen Free) |                          |

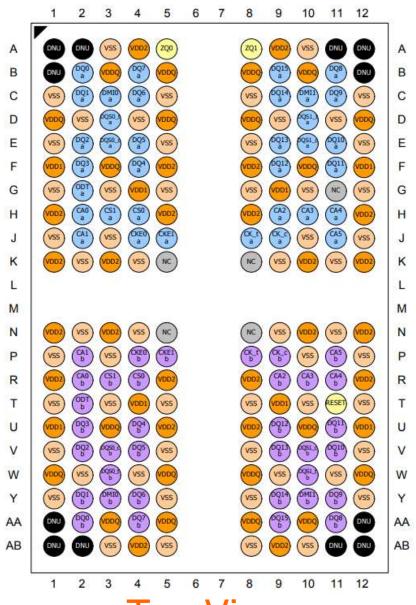

# 2. Package ballout & Addressing

## 2.1. FBGA package

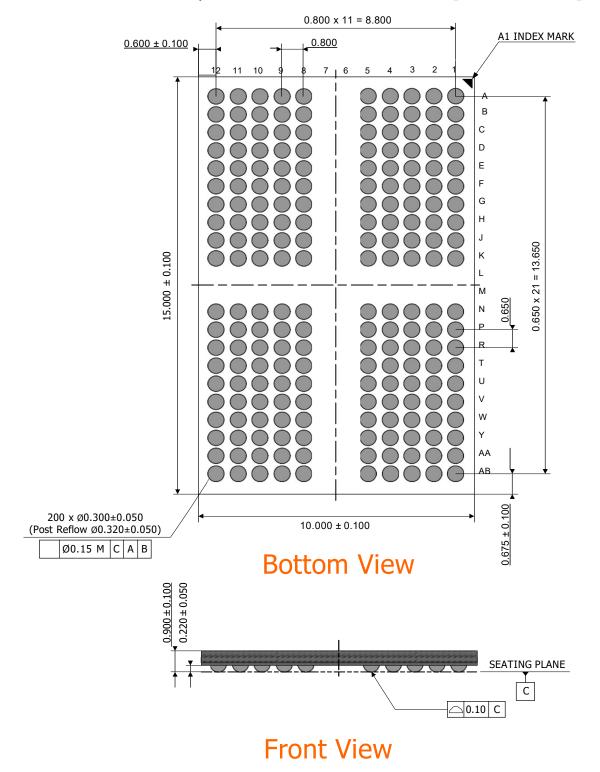

# 2.1.1. 200 balls, 10x15mm<sup>2</sup>, 0.8 x 0.65mm pitch

# Top View

# 200ball LPDDR4 (2CH) only

REV 1.0 5 **DLI Memory, Inc.** 08/2023

## **Mechanical specification**

200 Ball 0.65/0.80mm pitch 10.00mm x 15.00mm FBGA [t = 1.00mm max]

# **Pin Description**

| Symbol                    | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK_t, CK_c                | Input     | <b>Clock:</b> CK_t and CK_c are differential clock inputs. All address, command, and control input signals are sampled on the crossing of the positive edge of CK_t and the negative edge of CK_c. AC timings for CA parameters are referenced to CK.                                                                                                                                                                                                                            |

| CKE                       | Input     | <b>Clock Enable:</b> CKE HIGH activates and CKE LOW deactivates the internal clock circuits, input buffers, and output drivers. Power-saving modes are entered and exited via CKE transitions.                                                                                                                                                                                                                                                                                   |

| 66                        | Towns     | CKE is part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CS                        | Input     | Chip Select: CS is part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CA[5:0]                   | Input     | <b>Command/Address Inputs:</b> CA signals provide the Command and Address inputs according to the Command Truth Table.                                                                                                                                                                                                                                                                                                                                                           |

| ODT_CA_A<br>ODT_CA_B      | Input     | <b>CA ODT Control:</b> The ODT_CA pin is ignored by LPDDR4X devices. ODT-CS/CA/CK function is fully controlled through MR11 and M22. The ODT_CA pin shall be connected to either VDD2 or VSS.                                                                                                                                                                                                                                                                                    |

| DQ[15:0]                  | I/O       | Data Input/Output: Bi-direction data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DQS[1:0]_t,<br>DQS[1:0]_c | I/O       | <b>Data Strobe:</b> DQS_t and DQS_c are bi-directional differential output clock signals used to strobe data during a READ or WRITE. The Data Strobe is generated by the DRAM for a READ and is edge-aligned with Data. The Data Strobe is generated by the Memory Controller for a WRITE and must arrive prior to Data. Each byte of data has a Data Strobe signal pair.                                                                                                        |

| DMI[1:0]                  | I/O       | <b>Data Mask Inversion:</b> DMI is a bi-directional signal which is driven HIGH when the data on the data bus is inverted, or driven LOW when the data is in its normal state. Data Inversion can be disabled via a mode register setting. Each byte of data has a DMI signal. This signal is also used along with the DQ signals to provide write data masking information to the DRAM. The DMI pin function – Data Inversion or Data mask  - depends on Mode Register setting. |

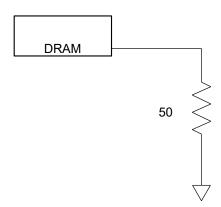

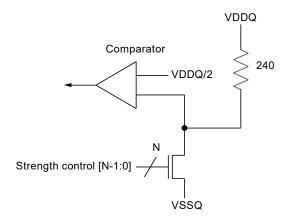

| ZQ                        | Reference | <b>Calibration Reference:</b> Used to calibrate the output drive strength and the termination resistance. There is one ZQ pin per die. The ZQ pin shall be connected to VDDQ through a $240\Omega \pm 1\%$ resistor.                                                                                                                                                                                                                                                             |

| VDDQ,<br>VDD1,<br>VDD2    | Supply    | Power Supplies: Isolated on the die for improved noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VSS, VSSQ                 | GND       | Ground Reference: Power supply ground reference                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RESET_n                   | Input     | <b>RESET:</b> When asserted LOW, the RESET_n signal resets all channels of the die. There is one RESET_n pad per die.                                                                                                                                                                                                                                                                                                                                                            |

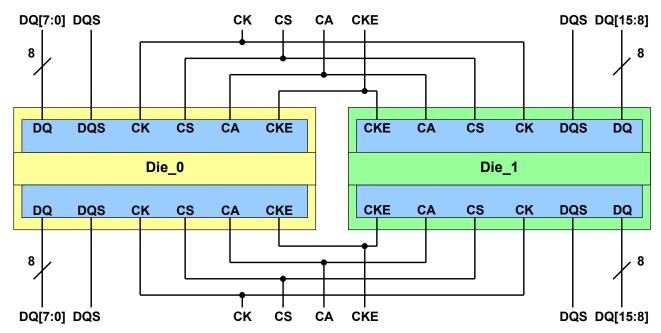

## 1. Functional Description

LPDDR4-SDRAM is a high-speed synchronous DRAM device internally configured with either 1 or 2 channels. Single-channel is comprised of 8-banks with from 1 Gb to 16 Gb per channel density. Dual-channel is comprised of 8-banks with from 2 Gb to 32 Gb per channel density. These devices contain the following number of bits:

Single-channel SDRAM devices contain the following number of bits:

4Gb has 4,294,967,296 bits

6Gb has 6,442,450,944 bits

8Gb has 8,589,934,592 bits

12Gb has 12,884,901,888 bits

16Gb has 17,179,869,184 bits

24Gb has 25,769,803,776 bits

32Gb has 34,359,738,368 bits

LPDDR4 devices use multi cycle of single data rate architecture on the Command/Address (CA) bus to reduce the number of input pins in the system. The 6-bit CA bus contains command, address and bank information. Each command uses two clock cycles, during which command information is transferred on positive edge of the corresponding clock.

These devices also use a double data rate architecture on the DQ pins to achieve high speed operation. The double data rate architecture is essentially an 16n prefetch architecture with an interface designed to transfer two data bits per DQ every clock cycle at the I/O pins. A single read or write access for the LPDDR4 SDRAM effectively consists of a single 16n-bit wide, one clock cycle data transfer at the internal DRAM core and eight corresponding n-bit wide, one-half-clock-cycle data transfers at the I/O pins.

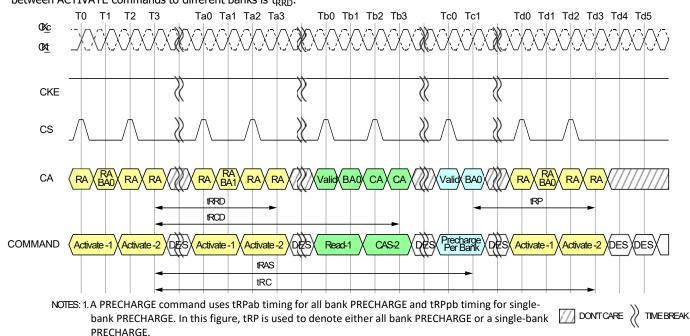

Read and write accesses to the LPDDR4 SDRAMs are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an Activate command, which is then followed by a Read or Write command. The address and BA bits registered coincident with the Activate command are used to select the row and the bank to be accessed. The address bits registered coincident with the Read, Write or Mask Write command are used to select the bank and the starting column location for the burst access.

Prior to normal operation, the LPDDR4 SDRAM must be initialized. The following section provides detailed information covering device initialization, register definition, command description and device operation

# 1.1. LPDDR4 SDRAM Addressing

Table 1 - LPDDR4 SDRAM x16 mode Addressing for Single Channel SDRAM Die

| М                            | lemory                                     |                                            |                                             |                                             |                                             |                                             |                                             |                                             |                                              |

|------------------------------|--------------------------------------------|--------------------------------------------|---------------------------------------------|---------------------------------------------|---------------------------------------------|---------------------------------------------|---------------------------------------------|---------------------------------------------|----------------------------------------------|

| De                           | ensity<br>er Die)                          | 1Gb                                        | 2Gb                                         | 3Gb                                         | 4Gb                                         | 6Gb                                         | 8Gb                                         | 12Gb                                        | 16Gb                                         |

| N                            | 1emory                                     |                                            |                                             |                                             |                                             |                                             |                                             |                                             |                                              |

| [                            | Density                                    | 1Gb                                        | 2Gb                                         | 3Gb                                         | 4Gb                                         | 6Gb                                         | 8Gb                                         | 12Gb                                        | 16Gb                                         |

| (per x                       | (16 channel)                               |                                            |                                             |                                             |                                             |                                             |                                             |                                             |                                              |

|                              | figuration                                 | 8Mb<br>x 16DQ<br>x 8 banks<br>x 1 channels | 16Mb<br>x 16DQ<br>x 8 banks<br>x 1 channels | 24Mb<br>x 16DQ<br>x 8 banks<br>x 1 channels | 32Mb<br>x 16DQ<br>x 8 banks<br>x 1 channels | 48Mb<br>x 16DQ<br>x 8 banks<br>x 1 channels | 64Mb<br>x 16DQ<br>x 8 banks<br>x 1 channels | 96Mb<br>x 16DQ<br>x 8 banks<br>x 1 channels | 128Mb<br>x 16DQ<br>x 8 banks<br>x 1 channels |

| Nι                           | ımber of                                   |                                            |                                             |                                             |                                             |                                             |                                             |                                             |                                              |

|                              | hannels<br>per die)                        | 1                                          | 1                                           | 1                                           | 1                                           | 1                                           | 1                                           | 1                                           | 1                                            |

| Νι                           | umber of                                   |                                            |                                             |                                             |                                             |                                             |                                             |                                             |                                              |

|                              | Banks                                      | 8                                          | 8                                           | 8                                           | 8                                           | 8                                           | 8                                           | 8                                           | 8                                            |

| (per                         | Channel)                                   |                                            |                                             |                                             |                                             |                                             |                                             |                                             |                                              |

| Array<br>Pre-Fetch<br>(bits, |                                            | 256                                        | 256                                         | 256                                         | 256                                         | 256                                         | 256                                         | 256                                         | 256                                          |

| <del></del>                  | channel)<br>umber of                       |                                            |                                             |                                             |                                             |                                             |                                             |                                             |                                              |

|                              | Rows                                       | 8,192                                      | 16,384                                      | 24,576                                      | 32,768                                      | 49,152                                      | 65,536                                      | 98,304                                      | 131,072                                      |

|                              | Channel)                                   |                                            |                                             |                                             |                                             |                                             |                                             |                                             |                                              |

| C                            | umber of<br>Columns<br>(fetch<br>undaries) | 64                                         | 64                                          | 64                                          | 64                                          | 64                                          | 64                                          | 64                                          | 64                                           |

|                              | age Size<br>(Bytes)                        | 2048                                       | 2048                                        | 2048                                        | 2048                                        | 2048                                        | 2048                                        | 2048                                        | 2048                                         |

| ]<br>(i                      | Channel<br>Density<br>Bits per<br>hannel)  | 1,073,741,824                              | 2,147,483,648                               | 3,221,225,472                               | 4,294,967,296                               | 6,442,450,944                               | 8,589,934,592                               | 12,884,901,88<br>8                          | 17,179,869,18<br>4                           |

| I                            | al Density<br>s per die)                   | 1,073,741,824                              | 2,147,483,648                               | 3,221,225,472                               | 4,294,967,296                               | 6,442,450,944                               | 8,589,934,592                               | 12,884,901,88<br>8                          | 17,179,869,18<br>4                           |

| _ `                          | k Address                                  | BA0 - BA2                                  | BA0 - BA2                                   | BA0 - BA2                                   | BA0 - BA2                                   | BA0 - BA2                                   | BA0 - BA2                                   | BA0 - BA2                                   | BA0 - BA2                                    |

| v16                          | Row<br>Addresses                           | R0 - R12                                   | R0 - R13                                    | R0 - R14<br>(R13=0 when<br>R14=1)           | R0 - R14                                    | R0 - R15<br>(R14=0 when<br>R15=1)           | R0 - R15                                    | R0 - R16<br>(R15=0 when<br>R16=1)           | R0 - R16                                     |

| x16                          | Column<br>Addresses                        | C0 - C9                                    | C0 - C9                                     | C0 - C9                                     | C0 - C9                                     | C0 - C9                                     | C0 - C9                                     | C0 - C9                                     | C0 - C9                                      |

| A                            | st Starting<br>Address<br>oundary          | 64 - bit                                   | 64 - bit                                    | 64 - bit                                    | 64 - bit                                    | 64 - bit                                    | 64 - bit                                    | 64 - bit                                    | 64 - bit                                     |

The lower two column addresses (C0 - C1) are assumed to be "zero" and are not transmitted on the CA bus.

- 1. Row and Column address values on the CA bus that are not used for a particular density are required to be at valid logic levels.

- 2. For non binary memory densities, only quarter of the row address space is invalid. When the MSB address bit is "HIGH", then the MSB 1 address bit must be "LOW".

- 3. The row address input which violates restriction described in note 3 in this table may result in undefined or vendor specific behavior. Consult memory vendor for more information.

- 4. For device densities not requiring R17 and R18, R17 and R18 must both be driven High for every ACT-2 command to maintain backward compatibility.

- 5. For device densities not requiring R18, R18 must be driven High for every ACT-2 command to maintain backward compatibility.

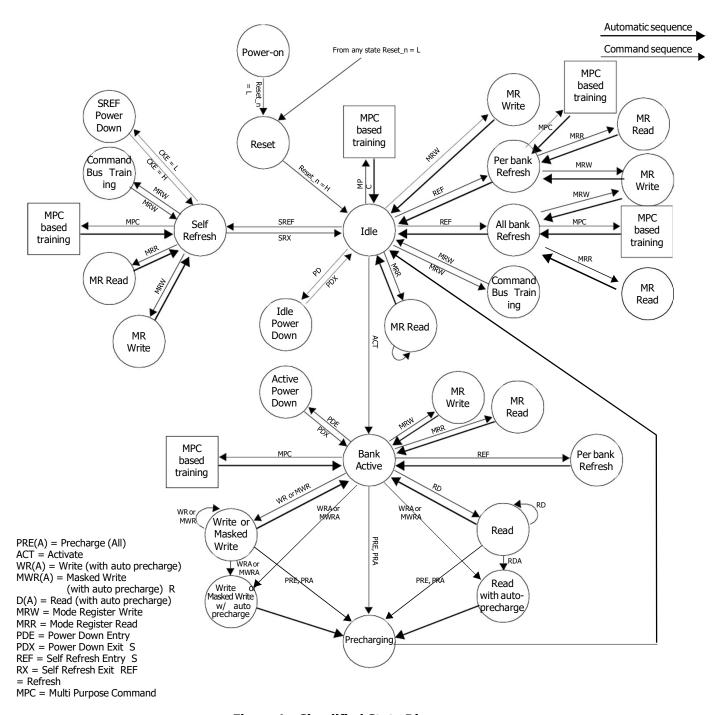

# 1.2. Simplified State Diagram

The state diagram provides a simplified illustration of the bus interface, supported state transitions, and the commands that control them. For a complete description of device behavior, use the information provided in the state diagram with the truth tables and tim- ing specifications. The truth tables describe device behavior and applicable restrictions when considering the actual state of all banks. For command descriptions, see the section

2. "Command Definitions and Timing Diagrams".

Figure 1 - Simplified State Diagram

REV 1.0 11 *DLI Memory, Inc.* 08/2023

Figure 2 - Simplified Bus Interface State Diagram

#### Notes

- 1. From the Self-Refresh state the device can enter Power-Down, MRR, MRW, or MPC states. See the section on Self-Refresh for more information.

- 2. In IDLE state, all banks are pre-charged.

- 3. In the case of a MRW command to enter a training mode, the state machine will not automatically return to the IDLE state at the conclusion of training. See the applicable training section for more information.

- 4. In the case of a MPC command to enter a training mode, the state machine may not automatically return to the IDLE state at the conclusion of training. See the applicable training section for more information.

- 5. This simplified State Diagram is intended to provide an overview of the possible state transitions and the commands to control them.

In particular, situations involving more than one bank, the enabling or disabling of on-die termination, and some other events are not captured in full detail.

- 6. States that have an "automatic return" and can be accessed from more than one prior state (Ex. MRW from either Idle or Active states) will return to the state from when they were initiated (Ex. MRW from Idle will return to Idle).

- 7. The RESET\_n pin can be asserted from any state, and will cause the SDRAM to go to the Reset State. The diagram shows RESET applied from the Power-On as an example, but the Diagram should not be construed as a restriction on RESET\_n.

REV 1.0 12 **DLI Memory, Inc.** 08/2023

# 1.3. Power-up and Initialization

For power-up and reset initialization, in order to prevent DRAM from functioning improperly, default values of the following MR set- tings are defined as following table.

Table 2 - LPDDR4 MRS defaults settings

| Item             | MRS          | Default setting | Description                     |  |  |

|------------------|--------------|-----------------|---------------------------------|--|--|

| FSP-OP/WR        | MR13 OP[7:6] | 00B             | FS-OP/WR[0] are enabled         |  |  |

| WLS              | MR2 OP[6]    | 0B              | Write Latency Set 0 is selected |  |  |

| WL               | MR2 OP[5:3]  | 000B            | WL = 4                          |  |  |

| RL               | MR2 OP[2:0]  | 000B            | RL = 6, nRTP = 8                |  |  |

| nWR              | MR1 OP[6:4]  | 000B            | nWR = 6                         |  |  |

| DBI-WR/RD        | MR3 OP[7:6]  | 00B             | Write & Read DBI are disabled   |  |  |

| CA ODT           | MR11 OP[6:4] | 000B            | CA ODT is disabled              |  |  |

| DQ ODT           | MR11 OP[2:0] | 000B            | DQ ODT is disabled              |  |  |

| VREF(CA) Setting | MR12 OP[6]   | 1B              | VREF(CA) Range[1] enabled       |  |  |

| VREF(CA) value   | MR12 OP[5:0] | 001101B         | Range1: 27.2% of VDD2           |  |  |

| VREF(DQ) Setting | MR14 OP[6]   | 1B              | VREF(DQ) Range[1] enabled       |  |  |

| VREF(DQ) Value   | MR14 OP[5:0] | 001101B         | Range1: 27.2% of VDDQ           |  |  |

Table 3 - LPDDR4x MRS defaults settings

| Item             | MRS          | Default setting | Description                     |

|------------------|--------------|-----------------|---------------------------------|

| FSP-OP/WR        | MR13 OP[7:6] | 00B             | FS-OP/WR[0] are enabled         |

| WLS              | MR2 OP[6]    | 0B              | Write Latency Set 0 is selected |

| WL               | MR2 OP[5:3]  | 000B            | WL = 4                          |

| RL               | MR2 OP[2:0]  | 000B            | RL = 6, nRTP = 8                |

| nWR              | MR1 OP[6:4]  | 000B            | nWR = 6                         |

| DBI-WR/RD        | MR3 OP[7:6]  | 00B             | Write & Read DBI are disabled   |

| CA ODT           | MR11 OP[6:4] | 000B            | CA ODT is disabled              |

| DQ ODT           | MR11 OP[2:0] | 000B            | DQ ODT is disabled              |

| VREF(CA) Setting | MR12 OP[6]   | 1B              | VREF(CA) Range[1] enabled       |

| VREF(CA) value   | MR12 OP[5:0] | 011101B         | Range1: 50.3% of VDDQ           |

| VREF(DQ) Setting | MR14 OP[6]   | 1B              | VREF(DQ) Range[1] enabled       |

| VREF(DQ) Value   | MR14 OP[5:0] | 011101B         | Range1: 50.3% of VDDQ           |

REV 1.0 13 **DLI Memory, Inc.** 08/2023

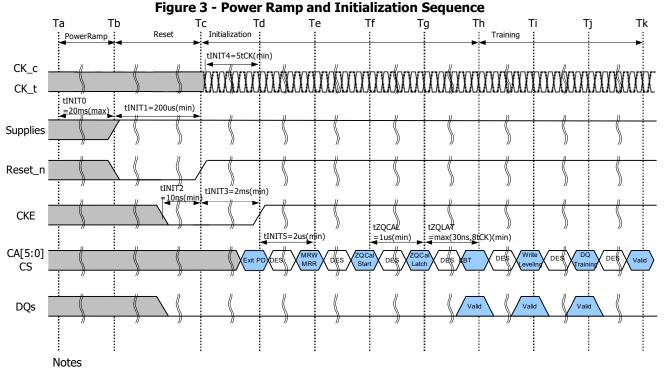

## 1.3.1. Voltage Ramp and Device Initialization

The following sequence shall be used to power up the LPDDR4 device. Unless specified otherwise, these steps are mandatory. Note that the power-up sequence of all channels must proceed simultaneously.

While applying power (after Ta), RESET\_n is recommended to be LOW (≤0.2 x VDD2) and all other inputs must be between VILmin and VIHmax. The device outputs remain at High-Z while RESET\_n is held LOW. Power supply voltage ramp requirements are provided in <u>Table "Voltage Ramp Conditions"</u>. VDD1 must ramp at the same time or earlier than VDD2. VDD2 must ramp at the same time or earlier than VDDQ.

**Table 4 - Voltage Ramp Conditions**

| After         | Applicable Conditions                  |

|---------------|----------------------------------------|

| Ta is reached | VDD1 must be greater than VDD2         |

|               | VDD2 must be greater than VDDQ - 200mV |

#### Notes

- 1. Ta is the point when any power supply first reaches 300mV.

- 2. Voltage ramp conditions in above table apply between Ta and power-off (controlled or uncontrolled).

- 3. Tb is the point at which all supply and reference voltages are within their defined ranges.

- 4. Power ramp duration tINIT0 (Tb-Ta) must not exceed 20ms.

- 5. The voltage difference between any of VSS and VSSQ pins must not excess 100mV.

REV 1.0 14 **DLI Memory, Inc.** 08/2023

- 2. Following the completion of the voltage ramp (Tb), RESET\_n must be maintained LOW. DQ, DMI, DQS\_t and DQS\_c voltage levels must be between Vssq and Vddq during voltage ramp to avoid latch-up. CKE, CK\_t, CK\_c, CS\_n and CA input levels must be between Vss and VDD2 during voltage ramp to avoid latch-up.

- 3. Beginning at Tb, RESET\_n must remain LOW for at least tINIT1(Tc), after which RESET\_n can be de-asserted to HIGH(Tc). At least 10ns before Reset\_n de-assertion, CKE is required to be set LOW. All other input signals are "Don't Care".

- Training is optional and may be done at the system architects discretion. The training sequence after ZQ\_CAL Latch(Th, Sequence7~9) in the above figure, is simplified recommendation and actual training sequence may vary depending on systems.

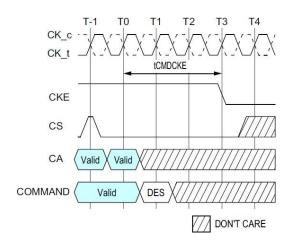

- 4. After RESET\_n is de-asserted(Tc), wait at least tINIT3 before activating CKE. Clock(CK\_t,CK\_c) is required to be started and stabilized for tINIT4 before CKE goes active(Td). CS is required to be maintained LOW when controller activates CKE.

- 5. After setting CKE high, wait minimum of tINIT5 to issue any MRR or MRW commands(Te). For both MRR and MRW commands, the clock frequency must be within the range defined for tCKb. Some AC parameters (for example, tDQSCK) could have relaxed timings (such as tDQSCKb) before the system is appropriately configured.

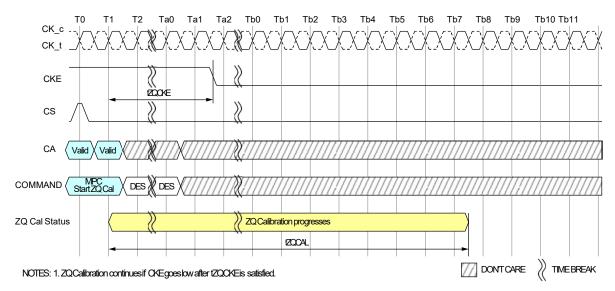

- 4. After completing all MRW commands to set the Pull-up, Pull-down and Rx termination values, the DRAM controller can issue ZQCAL Start command to the memory(Tf). This command is used to calibrate VOH level and output impedance over process, voltage and temperature. In systems where more than one LPDDR4 DRAM devices share one external ZQ resistor, the controller must not overlap the ZQ calibration sequence of each LPDDR4 device. ZQ calibration sequence is completed after tZQCAL (Tg) and the ZQCAL Latch command must be issued to update the DQ drivers and DQ+CA ODT to the calibrated values.

REV 1.0 08/2023 DLI Memory, Inc.

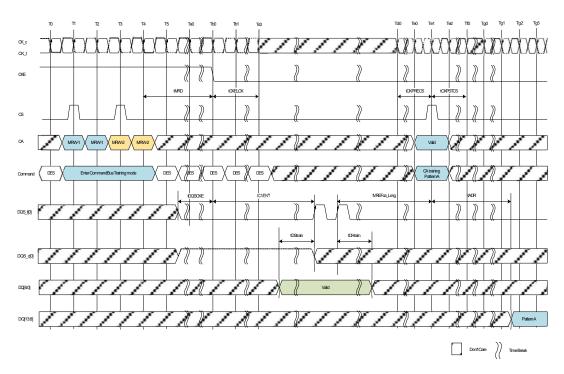

7. After tZQLAT is satisfied (Th) the command bus (internal VREF(CA), CS, and CA) should be trained for high-speed operation by issuing an MRW command (Command Bus Training Mode). This command is used to calibrate the device's internal VREF and align CS/CA with CK for high-speed operation. The LPDDR4 device will power-up with receivers configured for low-spee d

operations, and VREF(CA) set to a default factory setting. Normal device operation at clock speeds higher than tCKb may not be possible until command bus training has been completed.

The command bus training MRW command uses the CA bus as inputs for the calibration data stream, and outputs the results asynchronously on the DQ bus. See command bus training in the MRW section for information on how to enter/exit the training mode.

- 8. After command bus training, DRAM controller must perform write leveling. Write leveling mode is enabled when MR2 OP[7] is high(Ti). See write leveling section for detailed description of write leveling entry and exit sequence. In write leveling mode, the DRAM controller adjusts write DQS\_t/\_c timing to the point where the LPDDR4 device recognizes the start of write DQ data burst with desired write latency.

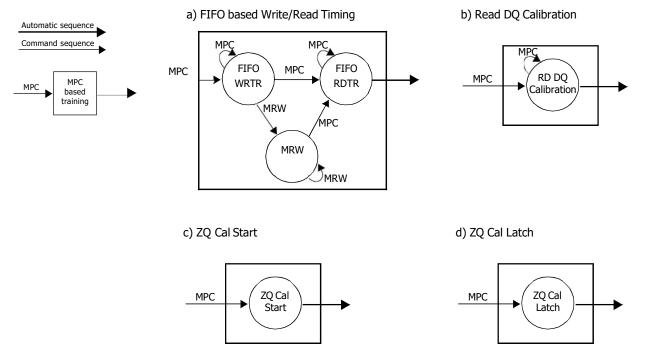

- 9. After write leveling, the DQ Bus (internal VREF(DQ), DQS, and DQ) should be trained for high-speed operation using the MPC training commands and by issuing MRW commands to adjust VREF(DQ)(Tj). The LPDDR4 device will power-up with receivers configured for low-speed operations and VREF(DQ) set to a default factory setting. Normal device operation at clock speeds higher than tCKb should not be attempted until DQ Bus training has been completed. The MPC Read Calibration command is used together with MPC FIFO Write/Read commands to train DQ bus without disturbing the memory array contents. See DQ Bus Training section for detailed DQ Bus Training sequence.

- 10.At Tk the LPDDR4 device is ready for normal operation, and is ready to accept any valid command. Any more registers that have not previously been set up for normal operation should be written at this time.

**Table 5 - Initialization Timing Parameters**

| Parameter    | Value          |           | Unit | Comment                                                   |

|--------------|----------------|-----------|------|-----------------------------------------------------------|

| i didilictei | Min            | Max       | Jine | Comment                                                   |

| tINIT0       |                | 20        | ms   | Maximum Voltage Ramp Time                                 |

| tINIT1       | 200            |           | us   | Minimum RESET_n LOW time after completion of voltage ramp |

| tINIT2       | 10             |           | ns   | Minimum CKE LOW time before RESET_n goes HIGH             |

| tINIT3       | 2              |           | ms   | Minimum CKE LOW time after RESET_n goes HIGH              |

| tINIT4       | 5              |           | tCK  | Minimum stable clock before first CKE HIGH                |

| tINIT5       | 2              |           | us   | Minimum idle time before first MRW/MRR command            |

| tZQCAL       | 1              |           | us   | ZQ Calibration time                                       |

| tZQLAT       | Max(30ns.8tCK) |           | ns   | ZQCAL latch quite time                                    |

| tCKb         | Note 1, 2      | Note 1, 2 | ns   | Clock cycle time during boot                              |

- 1. Min tCKb guaranteed by DRAM test is 18ns.

- 2. The system may boot at a higher frequency than dictated by min tCKb. The higher boot frequency is system dependent

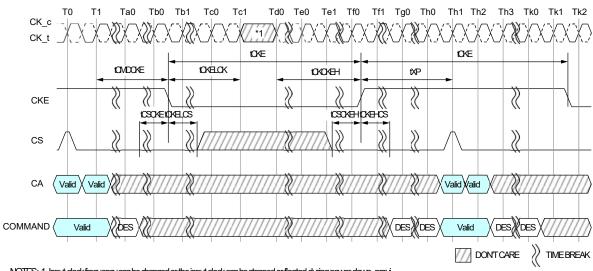

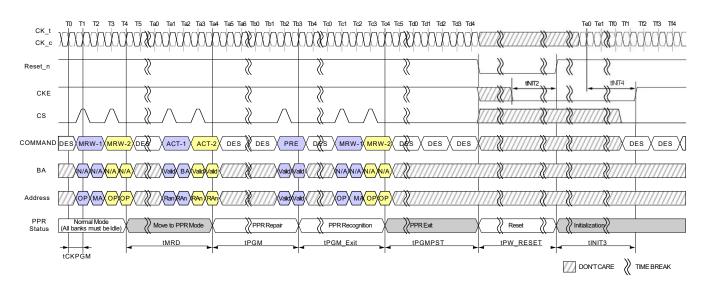

#### 1.3.2. Reset Initialization with Stable Power

The following sequence is required for RESET at no power interruption initialization.

- 1. Assert RESET\_n below 0.2 x VDD2 anytime when reset is needed. RESET\_n needs to be maintained for minimum tPW\_RESET. CKE must be pulled LOW at least 10 ns before de-asserting RESET\_n.

- 2. Repeat steps 4 to 10 in 1.3.1. "Voltage Ramp and Device Initialization".

**Table 6 – Reset Timing Parameter**

| Parameter   | Value |     | Unit  | Comment                                                             |

|-------------|-------|-----|-------|---------------------------------------------------------------------|

| raiailletei | Min   | Max | Oilit | Comment                                                             |

| tPW_RESET   | 100   | -   | ns    | Minimum RESET_n low time for Reset Initialization with stable power |

## 1.3.3. Power-off Sequence

The following procedure is required to power off the device.

While powering off, CKE must be held LOW (≤0.2 X VDD2) and all other inputs must be between VILmin and VIHmax. The device outputs remain at High-Z while CKE is held LOW. DQ, DMI, DQS\_t and DQS\_c voltage levels must be between VSSQ and VDDQ during voltage ramp to avoid latch-up. RESET\_n, CK\_t, CK\_c, CS and CA input levels must be between VSS and VDD2 during voltage ramp to avoid latch-up.

Tx is the point where any power supply drops below the minimum value specified.

Tz is the point where all power supplies are below 300mV. After TZ, the device is powered off.

**Table 7 - Power Supply Conditions for Power-off**

| Between   | Applicable Conditions                  |

|-----------|----------------------------------------|

| TX and TZ | VDD1 must be greater than VDD2         |

| IX and IZ | VDD2 must be greater than VDDQ - 200mV |

### Notes

1. The voltage difference between any of VSS, VSSQ pins must not exceed 100mV

REV 1.0 08/2023 DLI Memory, Inc.

## 1.3.4. Uncontrolled Power-off Sequence

When an uncontrolled power-off occurs, the following conditions must be met:

At Tx, when the power supply drops below the minimum values specified, all power supplies must be turned off and all power supply current capacity must be at zero, except any static charge remaining in the system.

After Tz (the point at which all power supplies first reach 300mV), the device must power off. During this period the relative voltage between power supplies is uncontrolled. VDD1 and VDD2 must decrease with a slope lower than 0.5V/µs between Tx and Tz.

An uncontrolled power-off sequence can occur a maximum of 400 times over the life of the device.

**Table 8 - Timing Parameters for Power-off**

| Symbol | Value |     | Unit  | Comment                     |

|--------|-------|-----|-------|-----------------------------|

| Symbol | Min   | Max | Oilit | Comment                     |

| tPOFF  | -     | 2   | S     | Maximum Power-off ramp time |

REV 1.0 18 **DLI Memory, Inc.** 08/2023

# 1.4. Mode Register Definition

Table below shows the mode registers for LPDDR4 SDRAM. Each register is denoted as "R" if it can be read but not written "W" if it can be written but not read, and "R/W" if it can be read and written. A Mode Register Read command is used to read a mode register. A Mode Register Write command is used to write a mode register.

**Table 9 - Mode Register Assignment (LPDDR4)**

| MR# | OP7                           | OP6           | OP5          | OP4               | OP3             | OP2         | OP1          | OP0          |  |  |

|-----|-------------------------------|---------------|--------------|-------------------|-----------------|-------------|--------------|--------------|--|--|

| 0   | CATR                          | SCLS          | SE mode      | RZ                | QI              | RFM support | Latency Mode | Refresh Mode |  |  |

| 1   | RPST                          |               | nWR (for AP) |                   | RD-PRE          | WR-PRE      | BL           |              |  |  |

| 2   | WR Lev                        | WLS           |              | WL                |                 |             | RL           |              |  |  |

| 3   | DBI-WR                        | DBI-RD        |              | PDDS              |                 | PPRP        | WR-PST       | PU-CAL       |  |  |

| 4   | TUF                           | Therma        | l Offset     | PPRE              | SR Abort        |             | Refresh Rate |              |  |  |

| 5   | LPDDR4 Manufacturer ID        |               |              |                   |                 |             |              |              |  |  |

| 6   |                               |               |              | Revision          | on ID-1         |             |              |              |  |  |

| 7   |                               |               |              | Revisio           | on ID-2         |             |              |              |  |  |

| 8   | IO W                          | Vidth         |              |                   | sity            |             | Ту           | pe           |  |  |

| 9   |                               |               |              |                   | fic Test Mode   |             |              |              |  |  |

| 10  |                               |               |              | RFU               |                 |             |              | ZQ Reset     |  |  |

| 11  | RFU                           |               | CA ODT       |                   | RFU             |             | DQ ODT       |              |  |  |

| 12  | CBT Modefor<br>Byte Mode      | VR-CA         |              |                   | VRE             | F(CA)       |              |              |  |  |

| 13  | FSP-OP                        | FSP-WR        | DMD          | RRO               | VRCG            | VRO         | RPT          | CBT          |  |  |

| 14  | RFU                           | VR(dq)        |              |                   | VRE             | (DQ)        |              |              |  |  |

| 15  |                               |               | Lov          | wer Byte Invert   | for DQ Calibrat | tion        |              |              |  |  |

| 16  |                               |               |              | PASR Ba           | ınk Mask        |             |              |              |  |  |

| 17  |                               |               |              |                   | ment Mask       |             |              |              |  |  |

| 18  |                               |               |              |                   | r Count - LSB   |             |              |              |  |  |

| 19  |                               |               |              |                   | r Count - MSB   |             |              |              |  |  |

| 20  |                               |               | Up           | per Byte Invert   |                 | tion        |              |              |  |  |

| 21  |                               |               |              |                   | <del>-</del> U  |             |              |              |  |  |

| 22  | OOTD for x8 2                 | ch(Byte) Mode | ODTD-CA      | ODTE-CS           | ODTE-CK         |             | SOC ODT      |              |  |  |

| 23  |                               |               | DQS Os       | cillator Interval | Timer Run Tim   | e Setting   |              |              |  |  |

| 24  | RAAMMT RAAIMT                 |               |              |                   |                 |             |              | RFM          |  |  |

| 25  | Post Package Repair Resources |               |              |                   |                 |             |              |              |  |  |

| 26  | Reserved for Future Use SCL   |               |              |                   |                 |             |              |              |  |  |

| 27  | Reserved for Future Use       |               |              |                   |                 |             |              |              |  |  |

| 28  |                               |               |              |                   | r Future Use    |             |              |              |  |  |

| 29  | Reserved for Future Use       |               |              |                   |                 |             |              |              |  |  |

| MR# | OP7                                             | OP6 | OP5   | OP4               | OP3              | OP2    | OP1 | ОР0 |  |  |  |

|-----|-------------------------------------------------|-----|-------|-------------------|------------------|--------|-----|-----|--|--|--|

| 30  | Reserved for Future Use                         |     |       |                   |                  |        |     |     |  |  |  |

| 31  | Bytemode Vref Selection Reserved for Future Use |     |       |                   |                  |        |     |     |  |  |  |

| 32  | DQ Calibration Pattern "a" (default = 5AH)      |     |       |                   |                  |        |     |     |  |  |  |

| 33  |                                                 |     |       | Do No             | ot Use           |        |     |     |  |  |  |

| 34  | Reserved for Future Use                         |     |       |                   |                  |        |     |     |  |  |  |

| 35  |                                                 |     |       | Reserved fo       | r Future Use     |        |     |     |  |  |  |

| 36  | Reserved for Future Use RAADEC                  |     |       |                   |                  |        |     |     |  |  |  |

| 37  |                                                 |     |       | Reserved fo       | r Future Use     |        |     |     |  |  |  |

| 38  | Reserved for Future Use                         |     |       |                   |                  |        |     |     |  |  |  |

| 39  | Reserved for testing - SDRAM will ignore        |     |       |                   |                  |        |     |     |  |  |  |

| 40  |                                                 |     | DQ Ca | alibration Patter | n "B" (default = | = 3CH) |     |     |  |  |  |

# Table 10 - Mode Register Assignment (LPDDR4x)

| MR#         OP7         OP6         OP5         OP4         PR2Q         RFU         RFU         RFU         RFU         RFU         RFU         RFU         RFU         RFU         RFST Mode         Refresh Mode           1         RRST         NWR (for AP)         WL         RD-PRE         WR-PRE         WR-PRE         REF           3         DBI-WR         DBI-RD         PDDS         PPRP         WR-PRE         PBPC           4         TUF         Thermal Offset         PPRE         SR Abort         Refresh Rate           5         FETTON TOTAL STATE                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |               |                |              | riouc itegistei    |                  | ,         |              |              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------|----------------|--------------|--------------------|------------------|-----------|--------------|--------------|

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MR# | OP7           | OP6            | OP5          | OP4                | OP3              | OP2       | OP1          | OP0          |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0   | Reserved      | RFU            | RFU          | RZ                 | QI               | RFU       | RFU          | Refresh Mode |

| DBI-WR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1   | RPST          |                | nWR (for AP) |                    | RD-PRE           | WR-PRE    | E            | BL           |

| 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2   | WR Lev        | WLS            |              | WL                 |                  |           | RL           |              |

| S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3   | DBI-WR        | DBI-RD         |              | PDDS               |                  | PPRP      | WR-PST       | PU-CAL       |

| Revision ID-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4   | TUF           | Therma         | al Offset    | PPRE               | SR Abort         |           | Refresh Rate |              |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5   |               |                |              | LPDDR4 Mar         | nufacturer ID    |           |              |              |

| 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6   |               |                |              | Revisio            | on ID-1          |           |              |              |

| Vendor Specific Test Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7   |               |                |              | Revisio            | on ID-2          |           |              |              |

| TREST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8   | IO V          | Vidth          |              | Der                | sity             |           | Ту           | rpe .        |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9   |               |                |              | Vendor Speci       | fic Test Mode    |           |              |              |

| 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10  |               |                |              | RFU                |                  |           |              | ZQ Reset     |

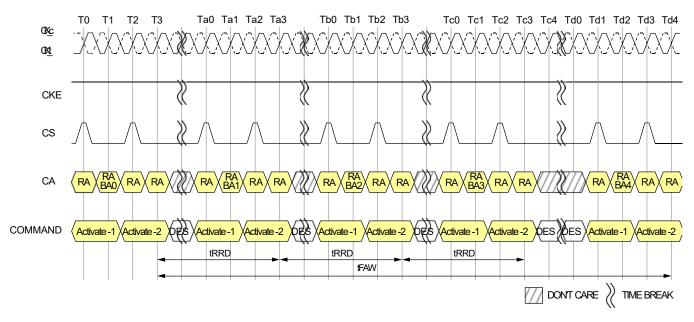

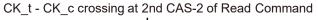

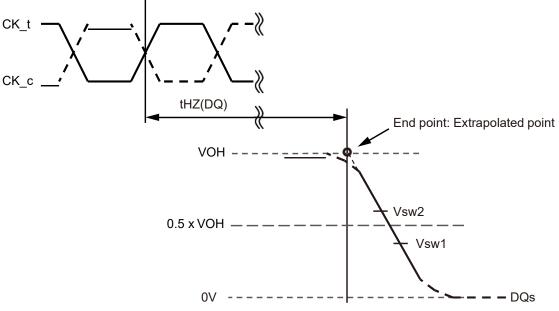

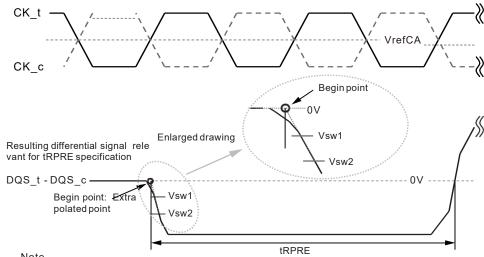

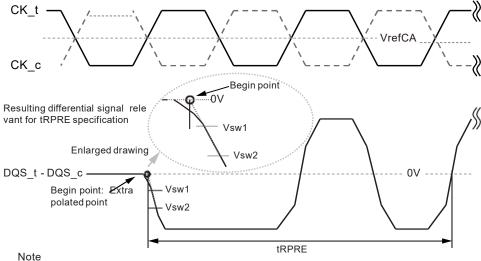

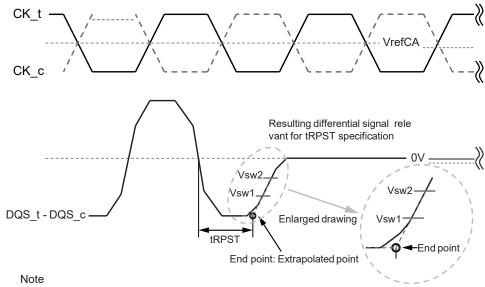

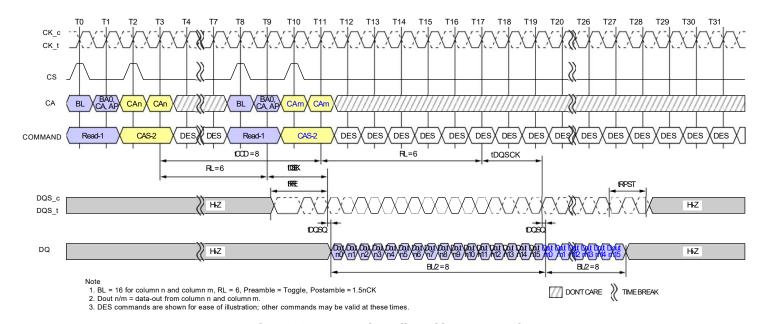

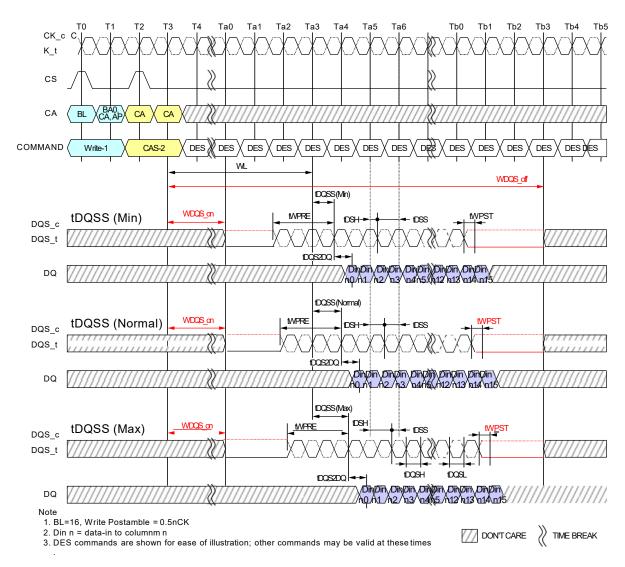

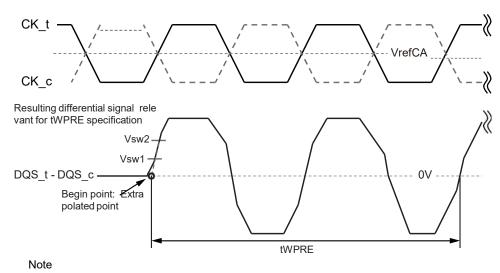

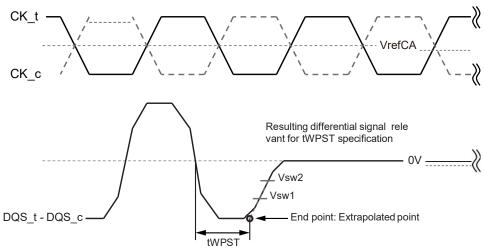

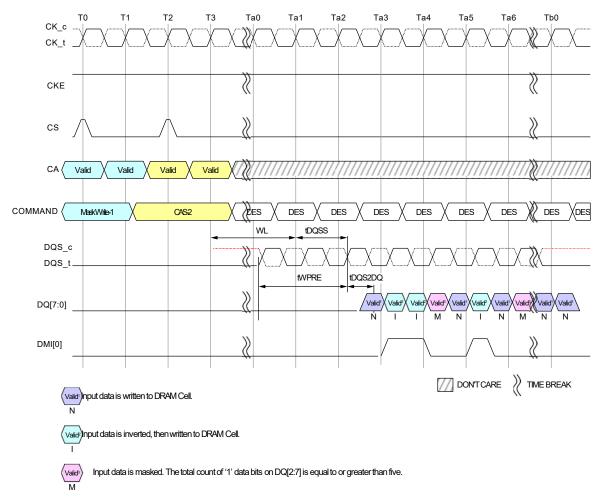

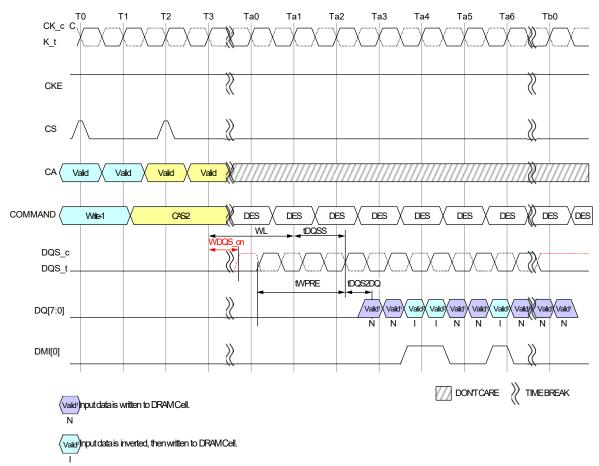

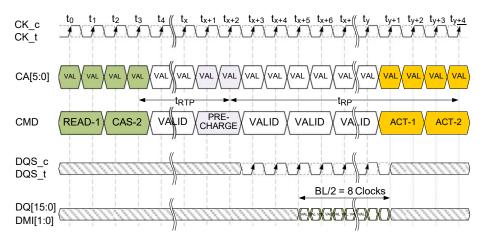

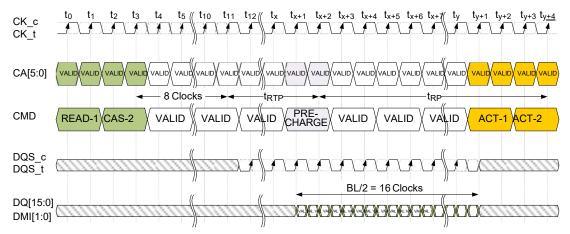

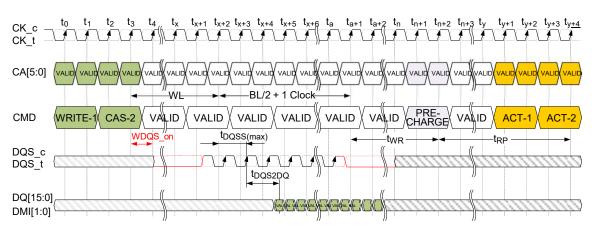

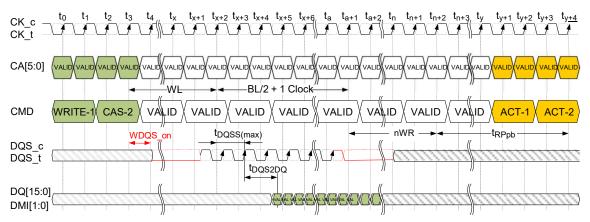

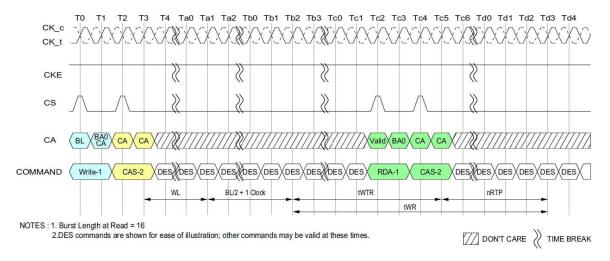

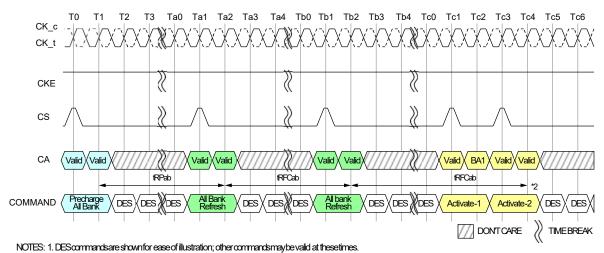

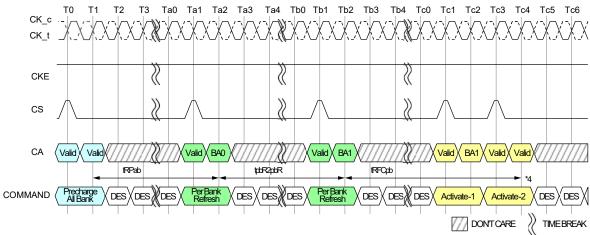

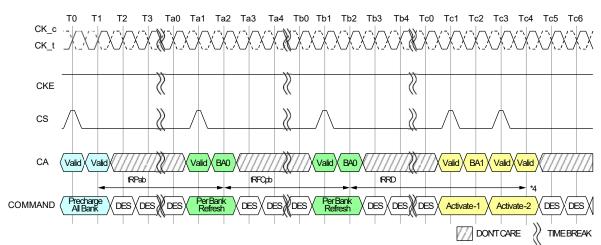

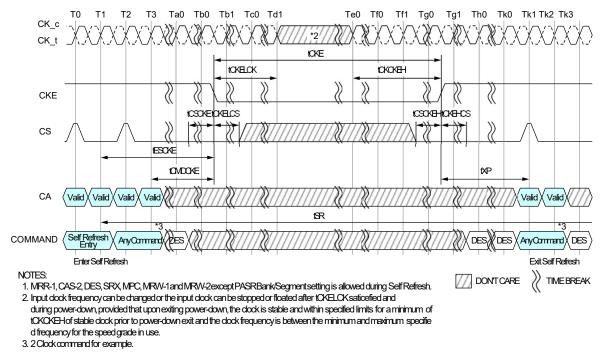

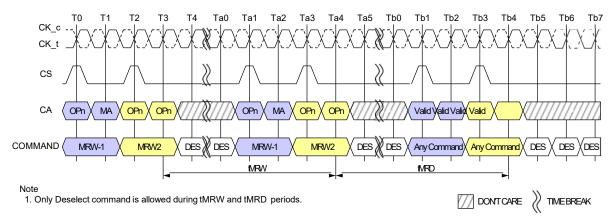

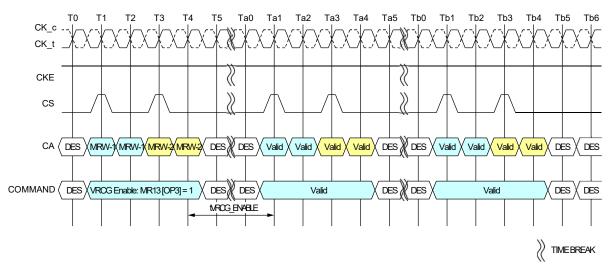

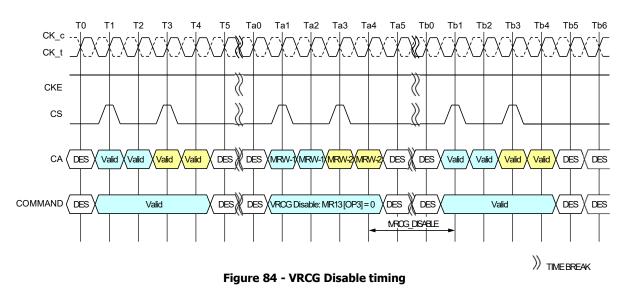

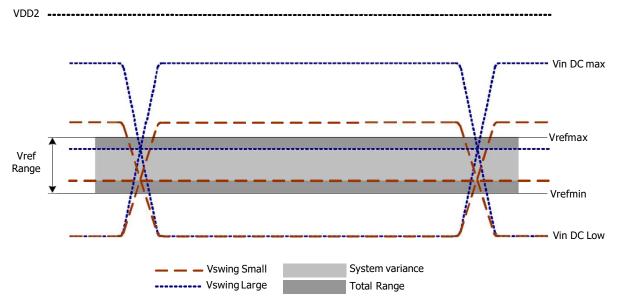

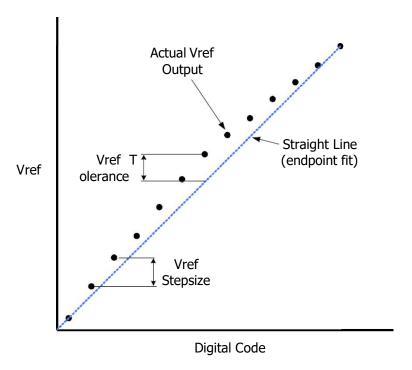

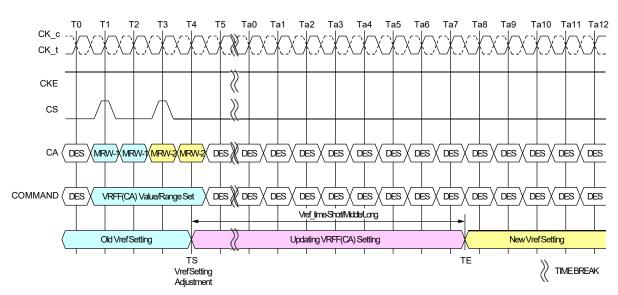

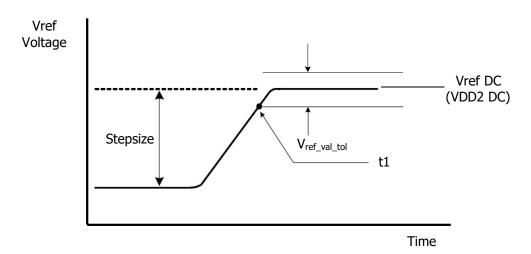

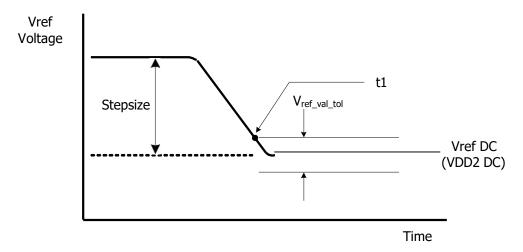

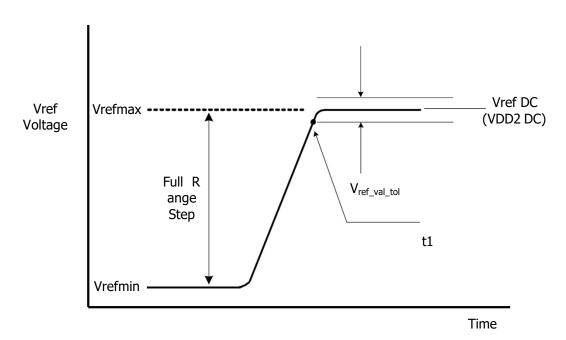

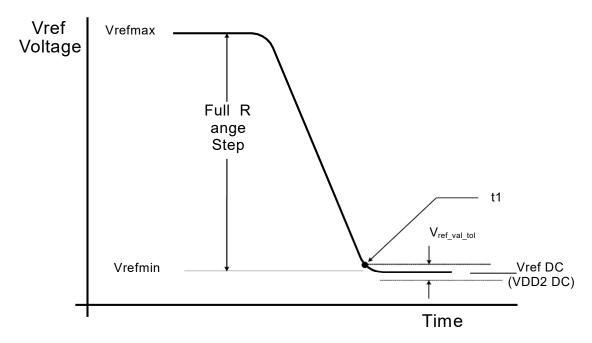

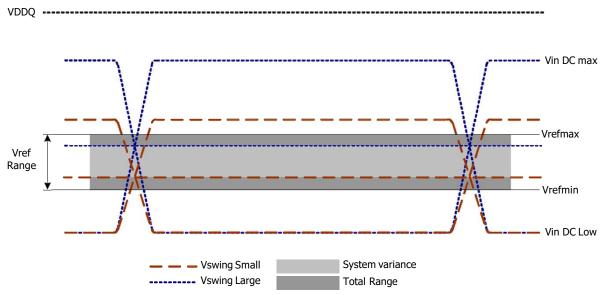

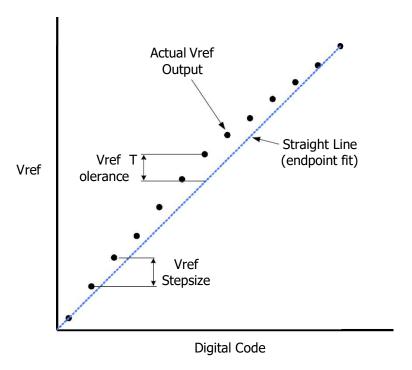

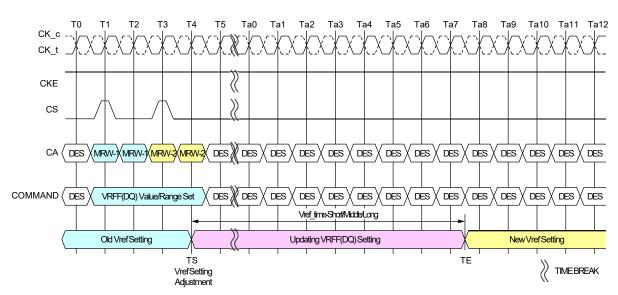

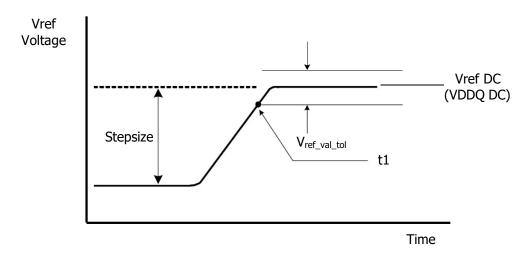

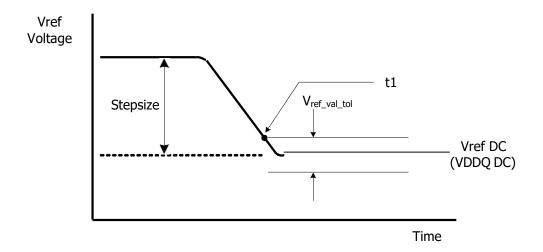

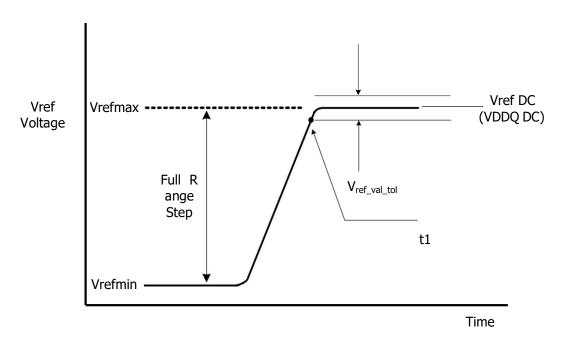

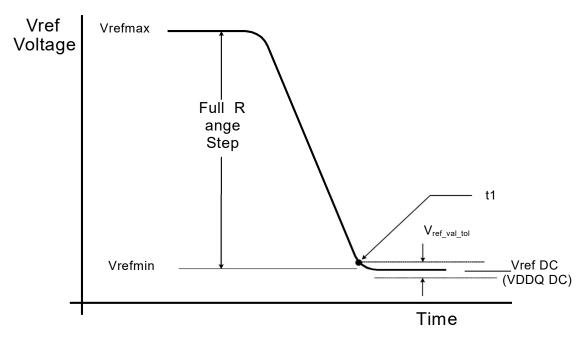

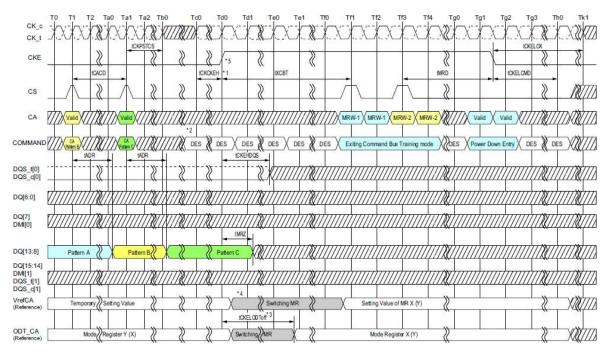

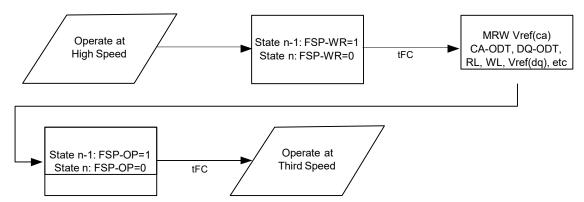

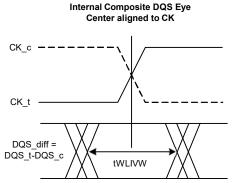

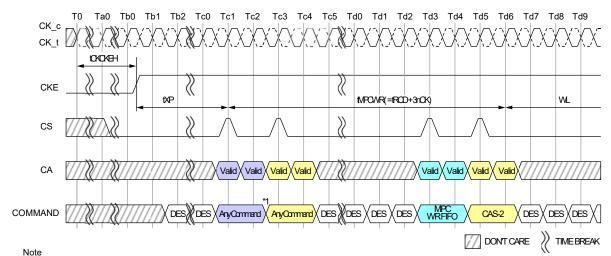

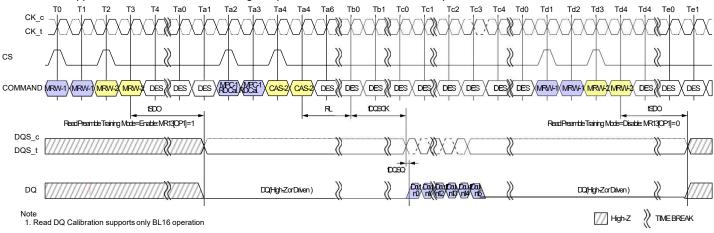

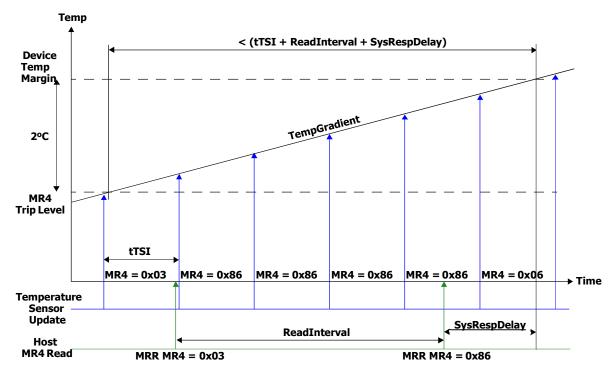

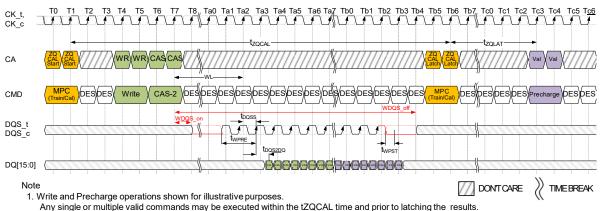

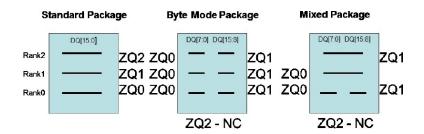

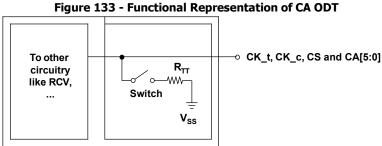

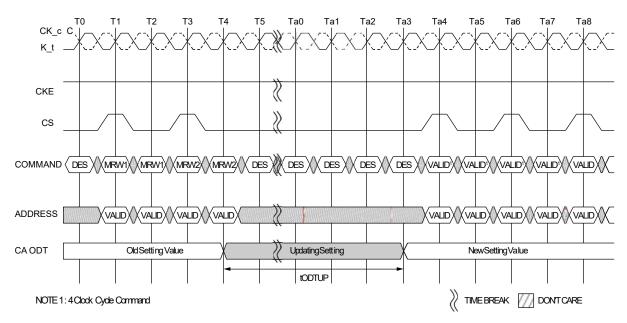

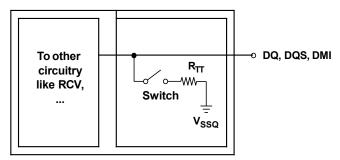

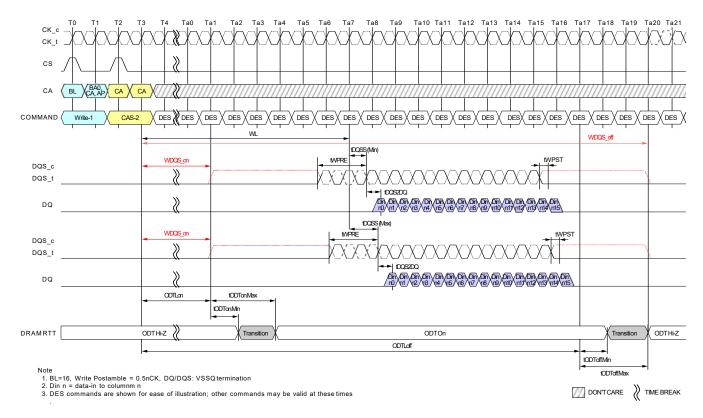

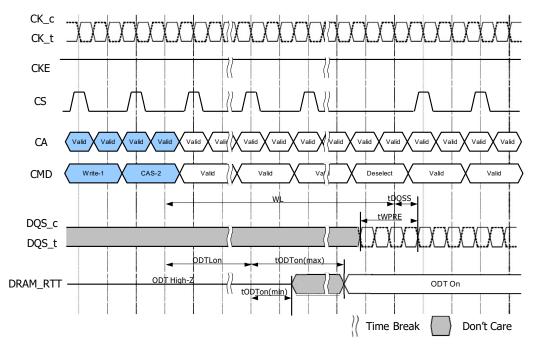

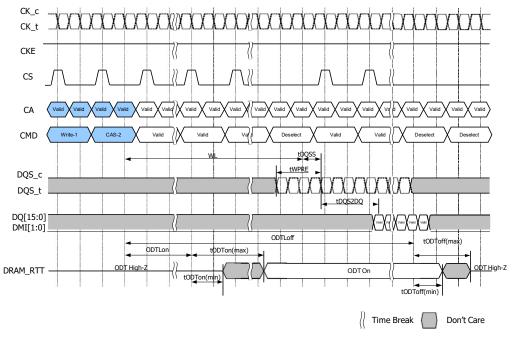

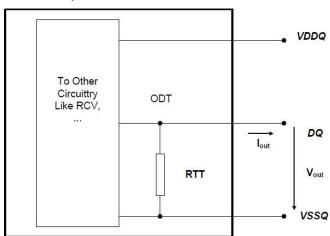

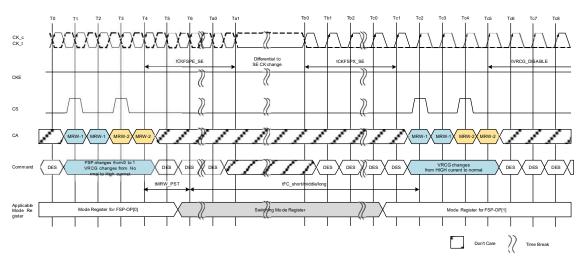

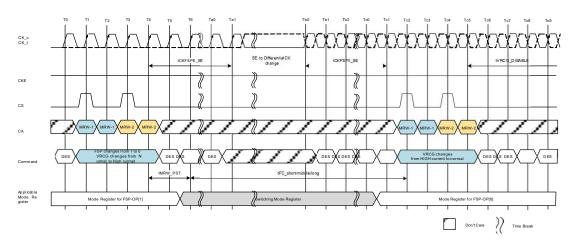

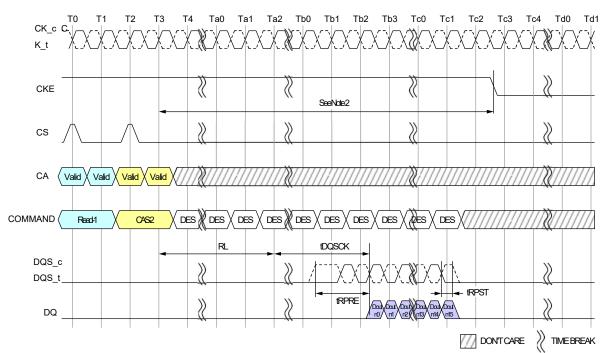

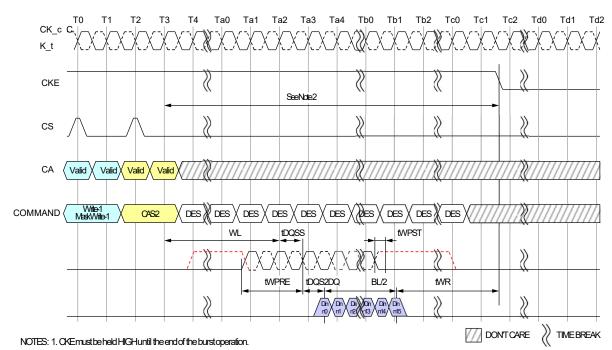

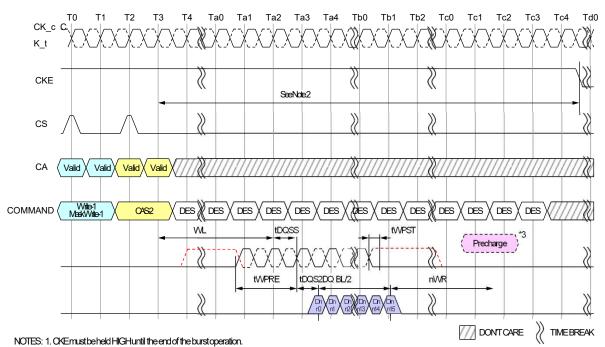

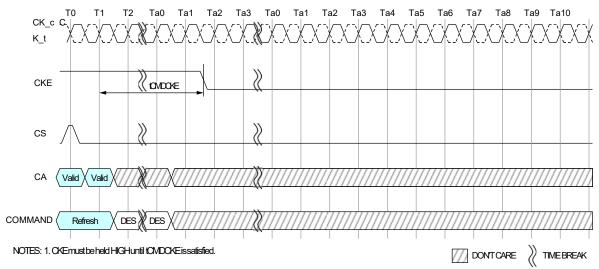

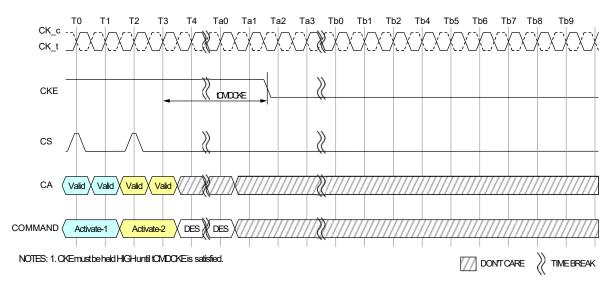

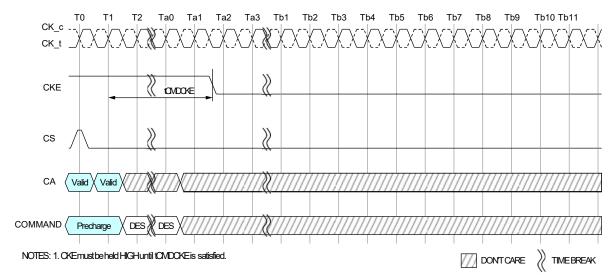

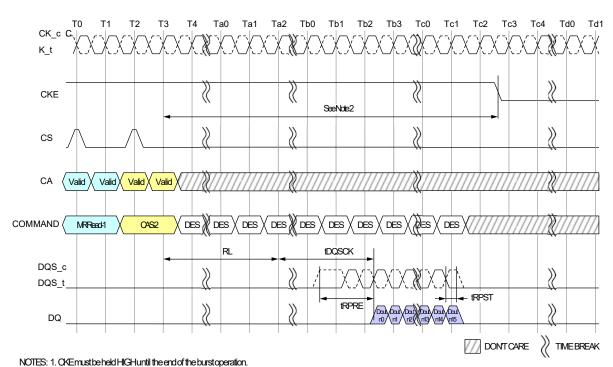

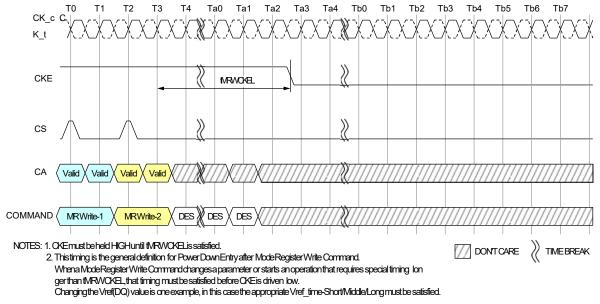

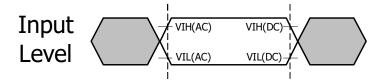

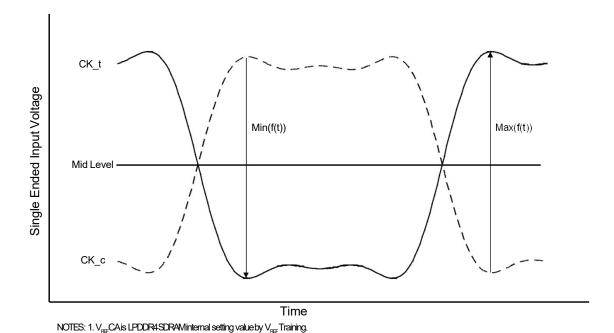

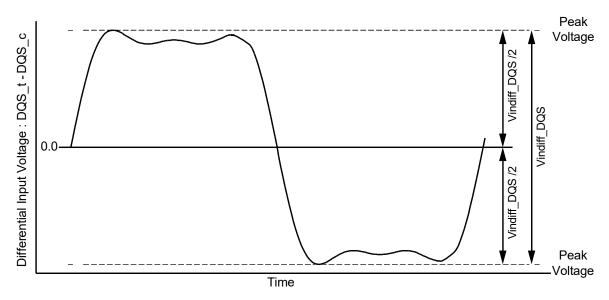

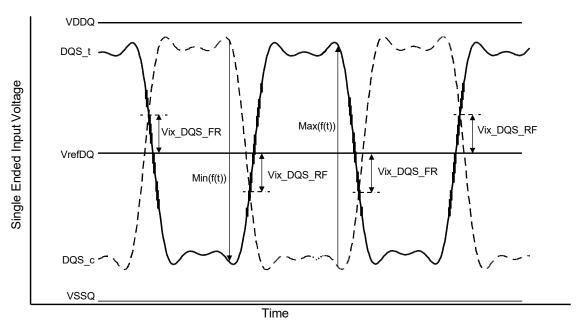

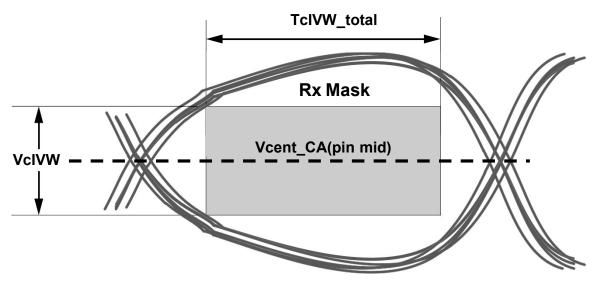

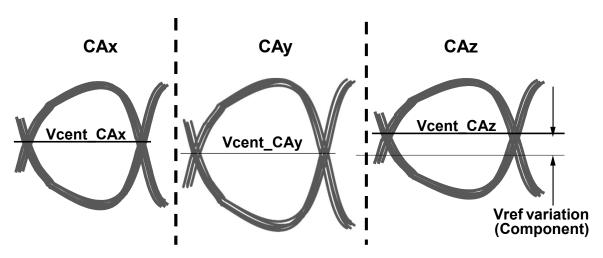

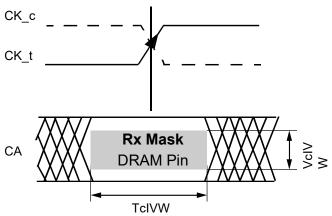

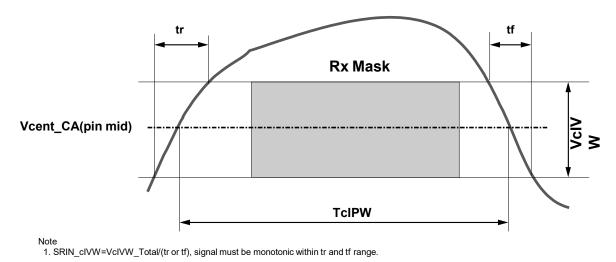

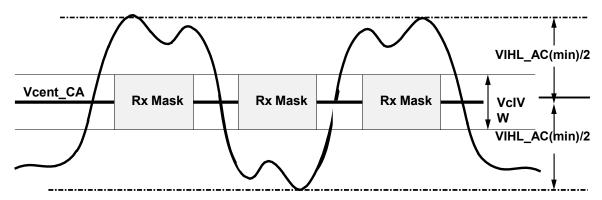

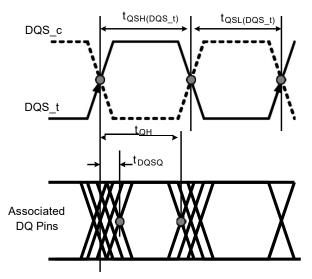

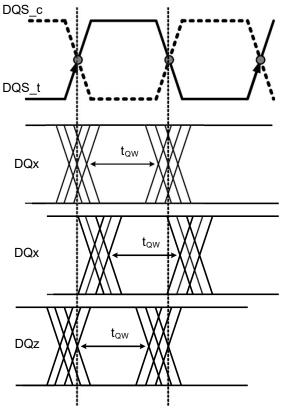

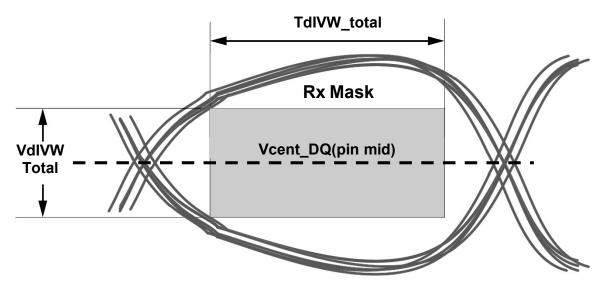

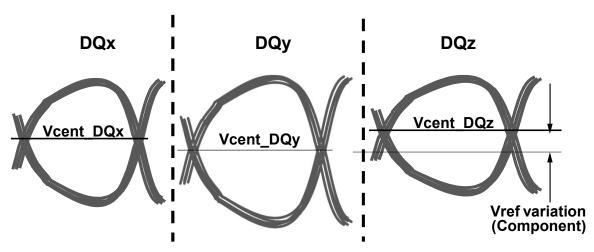

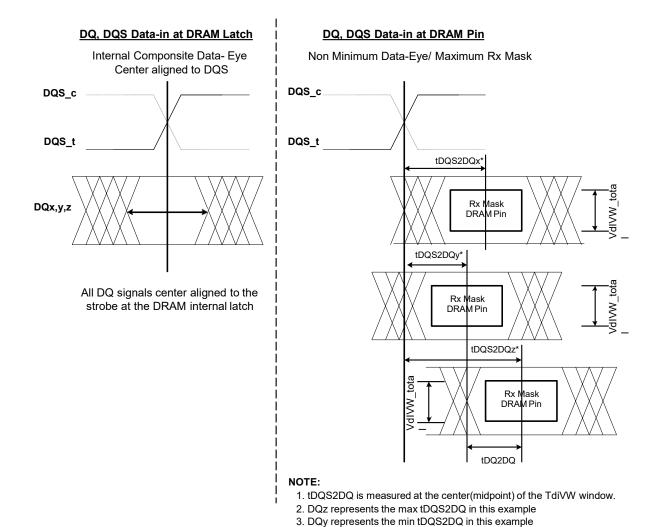

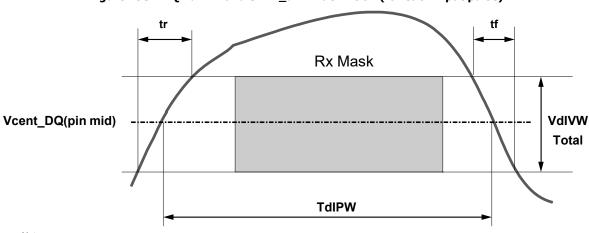

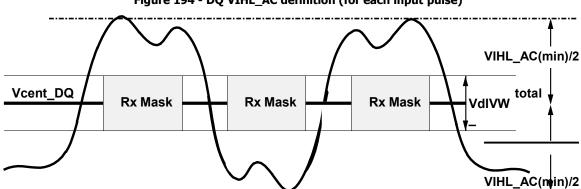

| 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11  | RFU           |                | CA ODT       |                    | RFU              |           | DQ ODT       |              |