# 178ball FBGA Specification

# **LPDDR3 16Gb SDRAM**

### **Features**

#### • Basis LPDDR3 Compliant

- Low Power Consumption

- 8n Prefetch Architecture and BL8 only

#### Signal Integrity

- Configurable DS for system compatibility

- Configurable On-Die Termination<sup>1</sup>

- ZQ Calibration for DS/ODT impedance accuracy via external ZQ pad ( $240\Omega\pm1\%$ )

### • Training for Signals' Synchronization

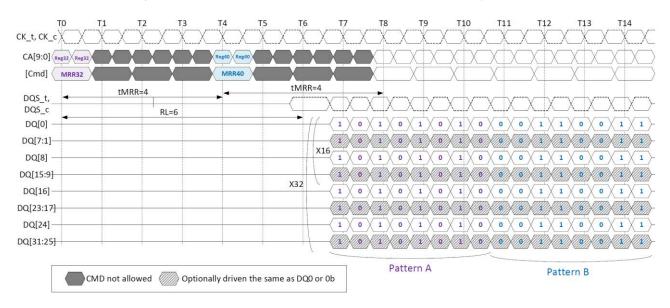

- DQ Calibration offering specific DQ output patterns

- CA Training

- Write Leveling via MR settings 2

#### Data Integrity

- DRAM built-in Temperature Sensor for Temperature Compensated Self Refresh (TCSR)

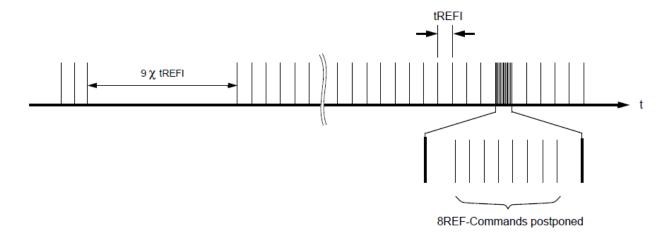

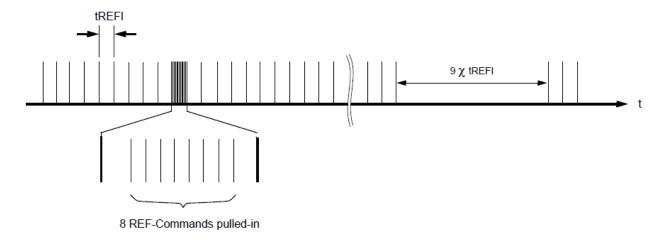

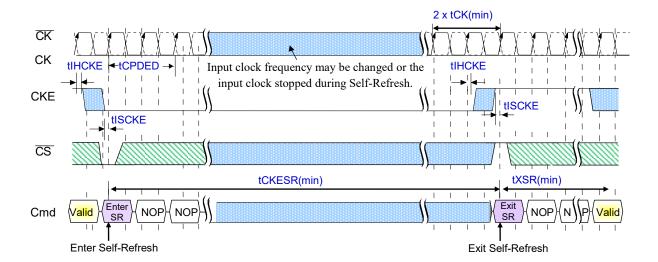

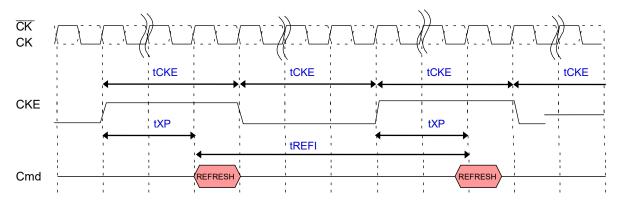

- Auto Refresh and Self Refresh Modes

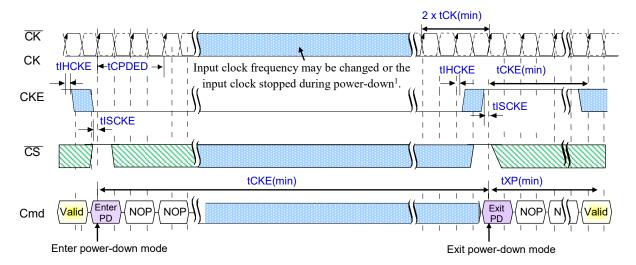

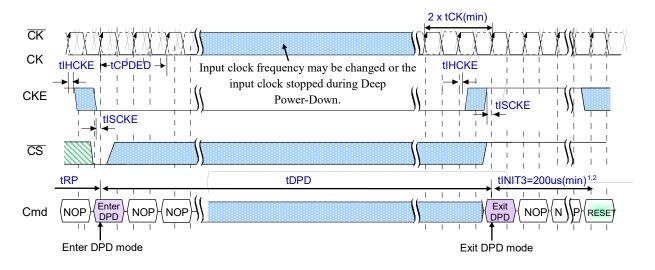

#### Power Saving Modes

- Deep Power Down Mode (DPD)

- Partial Array Self Refresh (PASR)

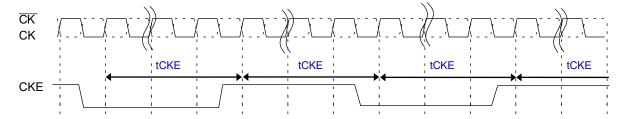

- Clock Stop capability during idle period

### HSUL12 interface and Power Supply

- VDD1= 1.70 to 1.95V

- VDD2/VDDQ/VDDCA = 1.14 to 1.3V

### **Programmable functions**

- Ron (Typical:34.3/40/48/60/80)

- R<sub>ON</sub> (PD34.3\_PU40 / PD40\_PU48 / PD34.3\_PU48)

- R<sub>TT</sub> (120/240)

- RL/WL Select (Set A / Set B)

- nWRE ( nWR≤9 / nWR>9)

- PASR (bank/segment)

### **Options**

### ■ Speed Grade (DataRate/Read Latency)

- 1866 Mbps / RL=14

### ■ Temperature Range (*Tc*)

- Commercial Grade : - 30°C to +105°C

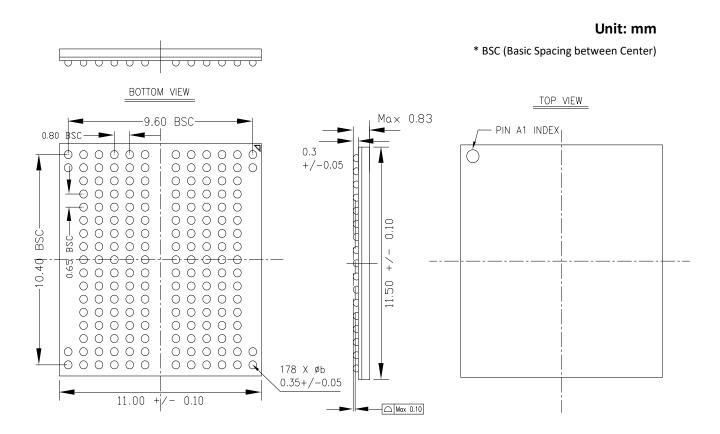

### ■ Package Information

Lead-free RoHS compliance and Halogen-free

| Items<br>(FBGA Package) | Width x Length x Height (mm) | Ball pitch<br>(mm) |

|-------------------------|------------------------------|--------------------|

| 178b (DDP)              | 11.00 x 11.50 x 0.83         | 0.65/0.80<br>Mixed |

### ■ Density, Signals and Addressing

| Items                                                     | 16Gb<br>(DDP)<br>X32 |

|-----------------------------------------------------------|----------------------|

| CS                                                        | <u>CS</u> [1:0]      |

| DQ                                                        | [31:0]               |

| DQS/DM                                                    | [3:0]/[3:0]          |

| CA                                                        | CA[9:0]              |

| Bank Addr.                                                | BA[2:0]              |

| Row Addr.3                                                | R[14:0]              |

| Column Addr.3                                             | C[9:0]               |

| Tc≦85°C                                                   | tREFI: 3.9µs         |

| 85°C <tc≦95°c< td=""><td>tREFI: 1.95µs</td></tc≦95°c<>    | tREFI: 1.95µs        |

| 95°C <tc≦105°c< td=""><td>tREFI: 0.975µs</td></tc≦105°c<> | tREFI: 0.975µs       |

NOTE 1 Depending on ballout, ODT pin may be NOT supported so ODT die pad is connected to Vss inside the package.

NOTE 2 Write Leveling DQ feedback on all DQs.

NOTE 3 Row and Column Addresses values on the CA bus that are not used are "don't care".

# **Ordering Information**

| Density Organization |                         |                    |          | Speed       |                         |    |  |  |  |  |

|----------------------|-------------------------|--------------------|----------|-------------|-------------------------|----|--|--|--|--|

|                      |                         | Part Number Packag |          | TCK<br>(ns) | Data Rate<br>(Mb/s/pin) | RL |  |  |  |  |

|                      | Commercial Grade        |                    |          |             |                         |    |  |  |  |  |

| 16Gb                 | 16Gb<br>(DDP) 512M x 32 | DM3N16GCALDF3-A8   | 170 Dall | 1.071       | 1866                    | 14 |  |  |  |  |

| (DDP)                |                         | DM3N16GCALDF3-A6   | 178-Ball | 1.250       | 1600                    | 12 |  |  |  |  |

# **Operating Frequency**

The backward compatibility of each frequency is listed in the following table. If an application operates at specific frequency which is not defined herein but within the highest and the lowest frequencies, then the comparative loose specifications to DRAM must be adopted from the neighboring defined frequency. Please confirm with DLI when the operating frequency is slower than the defined frequency.

| operating in equation to electron than t |      |      |      |      |      |

|------------------------------------------|------|------|------|------|------|

| Frequency[MHz]                           | 1066 | 933  | 800  | 667  |      |

| RL[nCK]                                  | 16   | 14   | 12   | 10   | Unit |

| VDDQ[V]                                  | 1.2  | 1.2  | 1.2  | 1.2  |      |

| DM3N16GCALDF3-A8                         | NA   | 1866 | 1600 | 1333 | Mhno |

| DM3N16GCALDF3-A6                         | NA   | NA   | 1600 | 1333 | Mbps |

#### Notes

Any part number also supports functional operation at lower frequencies as shown in the table which are not subject to Production Tests but has been verified.

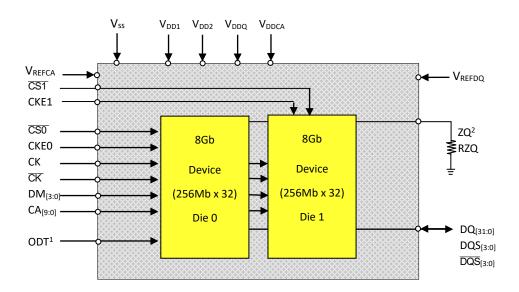

# Package Block Diagram

Signals of Dual Die, Single Channel Package Part Number: DM3N16GCALDF3-XXX

### Available: 178b

NOTE 1 ODT will be connected to rank0 (die0). The ODT input to rank1 (die1) will be connected to VSS in the package.

NOTE 2 ZQ is connected to both dies.

# **Ball Assignments**

# LPDDR3 178-ball FBGA DDP X32\_1ch

Part Number: DM3N16GCALDF3-XXX

< TOP View>

See the balls through the package

| A1 |     |       |       |        |      |      |   |      |      |      |        |      |     |   |

|----|-----|-------|-------|--------|------|------|---|------|------|------|--------|------|-----|---|

|    | 1   | 2     | 3     | 4      | 5    | 6    | 7 | 8    | 9    | 10   | 11     | 12   | 13  | - |

| Α  | DNU | DNU   | VDD1  | VDD1   | VDD1 | VDD1 |   | VDD2 | VDD2 | VDD1 | VDDQ   | DNU  | DNU | Α |

| В  | DNU | VSS   | ZQ    | NC     | VSS  | VSS  |   | DQ31 | DQ30 | DQ29 | DQ28   | VSS  | DNU | В |

| С  |     | CA9   | VSS   | NC     | VSS  | VSS  |   | DQ27 | DQ26 | DQ25 | DQ24   | VDDQ |     | С |

| D  |     | CA8   | VSS   | VDD2   | VDD2 | VDD2 |   | DM3  | DQ15 | DQS3 | DQS3   | VSS  |     | D |

| Е  |     | CA7   | CA6   | VSS    | VSS  | VSS  |   | VDDQ | DQ14 | DQ13 | DQ12   | VDDQ |     | Е |

| F  |     | VDDCA | CA5   | VSS    | VSS  | VSS  |   | DQ11 | DQ10 | DQ9  | DQ8    | VSS  |     | F |

| G  |     | VDDCA | VSS   | VSS    | VDD2 | VSS  |   | DM1  | VSS  | DQS1 | DQS1   | VDDQ |     | G |

| н  |     | VSS   | VDDCA | VREFCA | VDD2 | VDD2 |   | VDDQ | VDDQ | VSS  | VDDQ   | VDD2 |     | н |

| J  |     | CK    | СК    | VSS    | VDD2 | VDD2 |   | ODT  | VDDQ | VDDQ | VREFDQ | VSS  |     | J |

| К  |     | VSS   | CKE0  | CKE1   | VDD2 | VDD2 |   | VDDQ | NC   | VSS  | VDDQ   | VDD2 |     | К |

| L  |     | VDDCA | CS0   | CS1    | VDD2 | VSS  |   | DM0  | VSS  | DQS0 | DQS0   | VDDQ |     | L |

| М  |     | VDDCA | CA4   | VSS    | VSS  | VSS  |   | DQ4  | DQ5  | DQ6  | DQ7    | VSS  |     | М |

| N  |     | CA2   | CA3   | VSS    | VSS  | VSS  |   | VDDQ | DQ1  | DQ2  | DQ3    | VDDQ |     | N |

| Р  |     | CA1   | VSS   | VDD2   | VDD2 | VDD2 |   | DM2  | DQ0  | DQS2 | DQS2   | VSS  |     | Р |

| R  |     | CA0   | NC    | VSS    | VSS  | VSS  |   | DQ20 | DQ21 | DQ22 | DQ23   | VDDQ |     | R |

| Т  | DNU | VSS   | VSS   | VSS    | VSS  | VSS  |   | DQ16 | DQ17 | DQ18 | DQ19   | VSS  | DNU | Т |

| U  | DNU | DNU   | VDD1  | VDD1   | VDD1 | VDD1 |   | VDD2 | VDD2 | VDD1 | VDDQ   | DNU  | DNU | U |

| !  | 1   | 2     | 3     | 4      | 5    | 6    | 7 | 8    | 9    | 10   | 11     | 12   | 13  |   |

NOTE 1 Do Not Use (DNU)

NOTE 2 Top View, A1 in Top Left Corner

# SDP/DDP 178-ball Package Outline Drawing

Part Number: DM3N16GCALDF3-XXX

# **Ball Definition and Descriptions**

| Symbol                                                | Туре         | Function                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK, CK                                                | Input        | Clock: CK and $\overline{\text{CK}}$ are differential clock inputs. All Double Data Rate (DDR) CA inputs are sampled on both positive and negative edge of CK. Single Data Rate (SDR) inputs, $\overline{\text{CS}}$ and CKE, are sampled at the positive Clock edge.                            |

| CK, CK                                                | mput         | Clock is defined as the differential pair, CK and $\overline{\text{CK}}$ . The positive Clock edge is defined by the crosspoint of a rising CK and a falling $\overline{\text{CK}}$ . The negative Clock edge is defined by the crosspoint of a falling CK and a rising $\overline{\text{CK}}$ . |

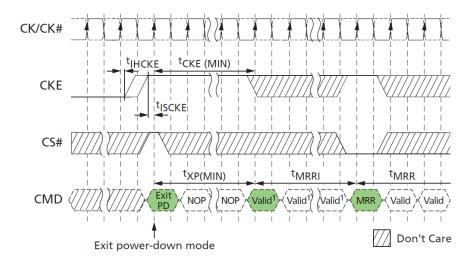

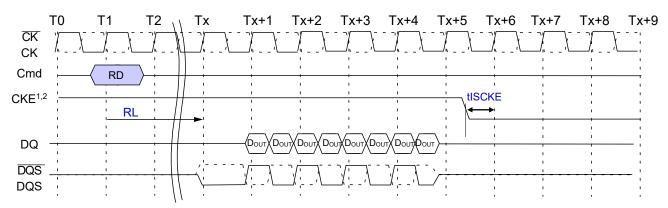

| CKE                                                   | Input        | <b>Clock Enable:</b> CKE HIGH activates and CKE LOW deactivates internal clock signals and therefore device input buffers and output drivers. Power savings modes are entered and exited through CKE transitions.                                                                                |

|                                                       |              | CKE is considered part of the command code. See Command Truth Table for command code descriptions. CKE is sampled at the positive Clock edge.                                                                                                                                                    |

| <u>CS</u>                                             | Input        | <b>Chip Select:</b> $\overline{CS}$ is considered part of the command code. See Command Truth Table for command code descriptions. $\overline{CS}$ is sampled at the positive Clock edge.                                                                                                        |

|                                                       |              | DDR Command/Address Inputs: Uni-directional command/address bus inputs.                                                                                                                                                                                                                          |

| CA[9:0]                                               | Input        | CA is considered part of the command code. See Command Truth Table for command code descriptions.                                                                                                                                                                                                |

| For x32<br>DM[3:0]                                    | Input        | Input Data Mask: DM is the input mask signal for write data. Input data is masked when DM is sampled HIGH coincident with that input data during a Write access. DM is sampled on both edges of DQS. Although DM is for input only, the DM loading shall match the DQ and DQS (or DQS).          |

| For x16<br>DM[3:2], DM[1:0]                           | ·            | For x32 devices, DM2 is the input data mask signal for the data on DQ16-23 and DM3 is the input data mask signal for the data on DQ24-31.                                                                                                                                                        |

| For x32<br>DQ[31:0]<br>For x16<br>DQ[31:16], DQ[15:0] | Input/output | Data Inputs/Output: Bi-directional data bus                                                                                                                                                                                                                                                      |

| For x32<br>DQS[3:0], <del>DQS</del> [3:0]             |              | Data Strobe (Bi-directional, Differential): The data strobe is bi-directional (used for read and write data) and differential (DQS and DQS). It is output with read data and input with write data.  DQS is edge-aligned to read data and centered with write data.                              |

| For x16 DQS[3:2], DQS[1:0] DQS[3:2], DQS[1:0]         | Input/output | For x32 DQS0 and $\overline{DQS0}$ correspond to the data on DQ0 - DQ7, DQS1 and $\overline{DQS1}$ to the data on DQ8 - DQ15, DQS2 and $\overline{DQS2}$ to the data on DQ16 - DQ23, DQS3 and $\overline{DQS3}$ to the data on DQ24 - DQ31.                                                      |

| ODT                                                   | Input        | On-Die Termination: This signal enables and disables termination on the DRAM DQ bus according to the specified mode register settings.                                                                                                                                                           |

| ZQ                                                    | Reference    | <b>External Reference ball for ZQ Calibration:</b> This ball is tied to an external 240 $\Omega$ resistor (RZQ), which is tied to V <sub>SS</sub> .                                                                                                                                              |

| V <sub>DD1</sub>                                      | Supply       | Core Power Supply 1: Core power supply                                                                                                                                                                                                                                                           |

| <b>V</b> DD2                                          | Supply       | Core Power Supply 2: Core power supply                                                                                                                                                                                                                                                           |

| VDDQ                                                  | Supply       | I/O Power Supply: Power supply for Data input/output buffers.                                                                                                                                                                                                                                    |

| VDDCA                                                 | Supply       | Input Receiver Power Supply: Power supply for CA0-9, CKE, CS, CK, and CK input buffers.                                                                                                                                                                                                          |

| VREFCA                                                | Supply       | Reference Voltage for CA Command and Control Input Receiver: Reference voltage for all CA0-9, CKE, $\overline{\text{CS}}$ , CK, and $\overline{\text{CK}}$ input buffers.                                                                                                                        |

| VREFDQ                                                | Supply       | Reference Voltage for DQ Input Receiver: Reference voltage for all data input buffers.                                                                                                                                                                                                           |

| Vss                                                   | Supply       | Ground                                                                                                                                                                                                                                                                                           |

| NC                                                    | -            | No Connect: No internal electrical connection is present.                                                                                                                                                                                                                                        |

NOTE 1: The signal may show up in a different symbol but it indicates to the same thing. e.g.,  $/CK = CK\# = \overline{CK} = CK\_n = CK\_c$ ,  $/DQS = DQS\# = \overline{DQS} = DQS\_b = DQS\_c$ ,  $/CS = CS\# = \overline{CS} = CSb = CS\_n$ .

NOTE 2: Data includes DQ and DM.

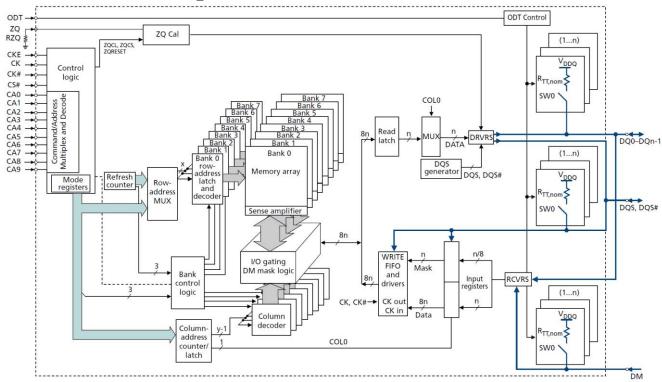

# **Functional Block Diagram**

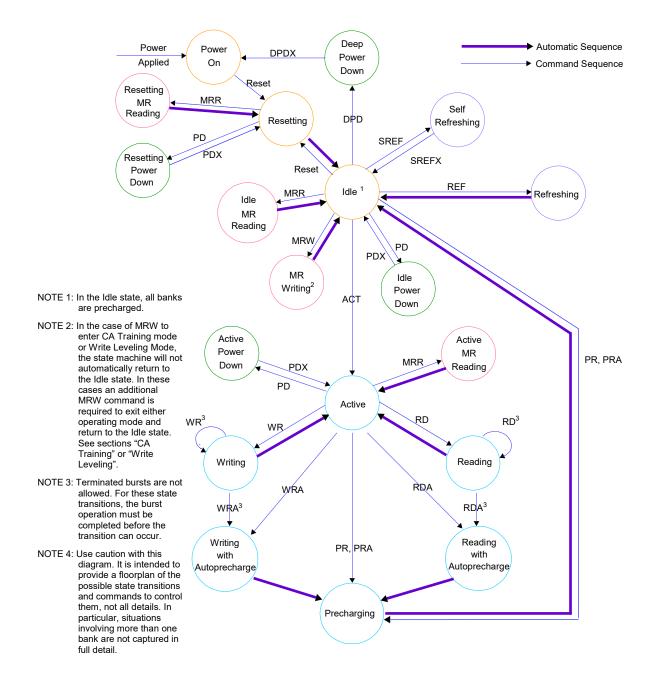

# **Simplified Bus Interface State Diagram**

LPDDR3-SDRAM state diagram provides a simplified illustration of allowed state transitions and the related commands to control them. For a complete definition of the device behavior, the information provided by the state diagram should be integrated with the truth tables and timing specification.

The truth tables provide complementary information to the state diagram, they clarify the device behavior and the applied restrictions when considering the actual state of all the banks.

### **Simplified State Diagram**

| Abbr. | Function                 | Abbr. | Function                              | Abbr. | Function           |

|-------|--------------------------|-------|---------------------------------------|-------|--------------------|

| ACT   | Active                   | PD    | Enter Power Down                      | SREF  | Enter self refresh |

| RD(A) | Read (w/ Autoprecharge)  | PDX   | Exit Power Down                       | SREFX | Exit self refresh  |

| WR(A) | Write (w/ Autoprecharge) | DPD   | Enter Deep Power Down                 |       |                    |

| PR(A) | Precharge (All)          | DPDX  | Exit Deep Power Down                  |       |                    |

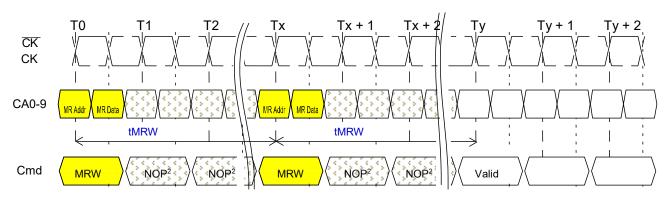

| MRW   | Mode Register Write      | REF   | Refresh                               |       |                    |

| MRR   | Mode Register Read       | RESET | Reset is achieved through MRW command |       |                    |

REV 1.0 10/2023 DLI Memory, Inc.

# **Absolute Maximum DC Ratings**

Stresses greater than those listed may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Absolute Maximum DC Ratings**

| Parameter                                                      | Symbol             | Min  | Max | Units | Notes |

|----------------------------------------------------------------|--------------------|------|-----|-------|-------|

| $V_{	extsf{DD1}}$ supply voltage relative to $V_{	extsf{SS}}$  | $V_{	extsf{DD1}}$  | -0.4 | 2.3 | V     | 1     |

| $V_{	extsf{DD2}}$ supply voltage relative to $V_{	extsf{SS}}$  | $V_{ m DD2}$       | -0.4 | 1.6 | V     | 1     |

| $V_{	exttt{DDCA}}$ supply voltage relative to $V_{	exttt{SS}}$ | $V_{	exttt{DDCA}}$ | -0.4 | 1.6 | V     | 1,2   |

| $V_{	extsf{DDQ}}$ supply voltage relative to $V_{	extsf{SS}}$  | $V_{	exttt{DDQ}}$  | -0.4 | 1.6 | V     | 1,3   |

| Voltage on any ball relative to $V_{ m SS}$                    | $V_{IN},V_{OUT}$   | -0.4 | 1.6 | V     |       |

| Storage Temperature                                            | $T_{STG}$          | -55  | 125 | °C    | 4     |

NOTE 1 See "Power-Ramp" section for relationships between power supplies.

NOTE 2  $V_{\text{REFCA}} \le 0.6 \text{ x } V_{\text{DDCA}}$ ; however,  $V_{\text{REFCA}}$  may be  $\ge V_{\text{DDCA}}$  provided that  $V_{\text{REFCA}} \le 300 \text{mV}$ .

NOTE 3  $V_{\text{REFDQ}} \le 0.7 \text{ x } V_{\text{DDQ}}$ ; however,  $V_{\text{REFDQ}}$  may be  $\ge V_{\text{DDQ}}$  provided that  $V_{\text{REFDQ}} \le 300 \text{mV}$ .

NOTE 4 Storage Temperature is the case surface temperature on the center/top side of the LPDDR3 device. For the measurement conditions, please refer to JESD51-2 standard.

### **AC/DC Operating Conditions**

Operation or timing that is not specified is illegal, and after such an event, in order to guarantee proper operation, the LPDDR3 device must be powered down and then restarted through the specialized initialization sequence before normal operation can continue.

### **Recommended DC Operating Conditions**

| Camab al           |      | Voltage |      | DDAM               | TI:4 |

|--------------------|------|---------|------|--------------------|------|

| Symbol             | Min  | Тур     | Max  | DRAM               | Unit |

| $V_{	extsf{DD1}}$  | 1.70 | 1.80    | 1.95 | Core Power1        | V    |

| $V_{ m DD2}$       | 1.14 | 1.20    | 1.30 | Core Power2        | V    |

| $V_{	exttt{DDCA}}$ | 1.14 | 1.20    | 1.30 | Input Buffer Power | V    |

| $V_{	exttt{DDQ}}$  | 1.14 | 1.20    | 1.30 | I/O Buffer Power   | V    |

NOTE 1  $V_{\rm DD1}$  uses significantly less current than  $V_{\rm DD2}$ .

NOTE 2 The voltage range is for DC voltage only. DC is defined as the voltage supplied at the DRAM and is inclusive of all noise up to 1MHz at the DRAM package ball.

### **Input Leakage Current**

| Parameter/Condition              | Symbol            | Min | Max | Unit | Notes |

|----------------------------------|-------------------|-----|-----|------|-------|

| Input Leakage current            | I <sub>L</sub>    | -2  | 2   | uA   | 1, 2  |

| $V_{REF}$ supply leakage current | I <sub>VREF</sub> | -1  | 1   | uA   | 3, 4  |

- NOTE 1 For CA, CKE,  $\overline{CS}$ , CK,  $\overline{CK}$ . Any input  $0V \le V_{IN} \le V_{DDCA}$  (All other pins not under test = 0V)

- NOTE 2 Although DM is for input only, the DM leakage shall match the DQ and DQS/ $\overline{\text{DQS}}$  output leakage specification.

- NOTE 3 The minimum limit requirement is for testing purposes. The leakage current on  $V_{\text{REFCA}}$  and  $V_{\text{REFDQ}}$  pins should be minimal.

- NOTE 4  $V_{\text{REFDQ}} = V_{\text{DDQ}}/2$  or  $V_{\text{REFCA}} = V_{\text{DDCA}}/2$ . (All other pins not under test = 0V)

- NOTE 5 The input leakage current of QDP: max/min = ±4uA, the Vref supply leakage current of QDP: max/min = ±2uA

### **Operating Temperature Range**

| Parameter/Condition | Symbol        | Min | Max | Unit |

|---------------------|---------------|-----|-----|------|

| Standard            | <b>T</b>      | -30 | 85  | ەر   |

| Elevated            | <b>I</b> OPER | 85  | 105 | ٠٠   |

- NOTE 1 Operating Temperature is the case surface temperature on the center-top side of the LPDDR3 device. For the measurement conditions, please refer to JESD51-2 standard.

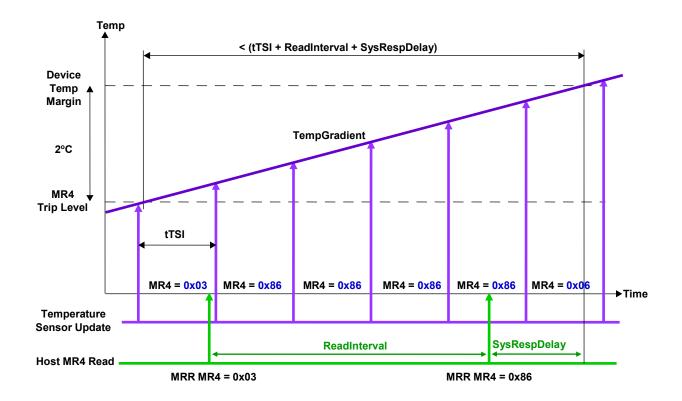

- NOTE 2 Some applications require operation of LPDDR3 in the maximum temperature conditions in the Elevated Temperature Range between 85°C and 105°C case temperature. For LPDDR3 devices, derating may be necessary to operate in this range. See MR4.

- NOTE 3 Either the device case temperature rating or the temperature sensor may be used to set an appropriate refresh rate, determine the need for AC timing de-rating and/or monitor the operating temperature. When using the temperature sensor, the actual device case temperature may be higher than the T<sub>OPER</sub> rating that applies for the Standard or Elevated Temperature Ranges. For example, T<sub>CASE</sub> may be above 85°C when the temperature sensor indicates a temperature of less than 85°C.

# **AC/DC Input Level**

### AC and DC Logic Input Levels for Single-Ended Signals

### Single-Ended AC and DC Input Levels for CA and $\overline{\text{CS}}$ Inputs

| Symbol Para             | Donomoton                                                  | 1333/                    | /1600                           | 1866                     | Unit                     | Notes |       |

|-------------------------|------------------------------------------------------------|--------------------------|---------------------------------|--------------------------|--------------------------|-------|-------|

|                         | Parameter                                                  | Min                      | Max                             | Min                      | Max                      | Unit  | Notes |

| V <sub>IHCA</sub> (AC)  | AC input logic high                                        | V <sub>Ref</sub> + 0.150 | Note 2                          | V <sub>Ref</sub> + 0.135 | Note 2                   | V     | 1, 2  |

| V <sub>ILCA</sub> (AC)  | AC input logic low                                         | Note 2                   | V <sub>Ref</sub> - 0.150        | Note 2                   | V <sub>Ref</sub> - 0.135 | V     | 1, 2  |

| V <sub>IHCA</sub> (DC)  | DC input logic high                                        | V <sub>Ref</sub> + 0.100 | $V_{	exttt{DDCA}}$              | V <sub>Ref</sub> + 0.100 | $V_{	extsf{DDCA}}$       | V     | 1     |

| V <sub>ILCA</sub> (DC)  | DC input logic low                                         | Vss                      | V <sub>Ref</sub> - 0.100        | Vss                      | V <sub>Ref</sub> - 0.100 | V     | 1     |

| V <sub>RefCA</sub> (DC) | Reference Voltage for CA and $\overline{\text{CS}}$ inputs | 0.49 * V <sub>DDCA</sub> | 0.51 * <i>V</i> <sub>DDCA</sub> | 0.49 * V <sub>DDCA</sub> | 0.51 * V <sub>DDCA</sub> | V     | 3, 4  |

NOTE 1 For CA and  $\overline{\text{CS}}$  input only pins.  $V_{\text{Ref}} = V_{\text{RefCA(DC)}}$ .

NOTE 2 Overshoot and Undershoot Specifications.

NOTE 3 The ac peak noise on  $V_{\text{RefCA}}$  may not allow  $V_{\text{RefCA}}$  to deviate from  $V_{\text{RefCA}(DC)}$  by more than  $\pm$  1%  $V_{\text{DDCA}}$  (for reference:

approx. ± 12 mV).

NOTE 4 For reference: approx.  $V_{DDCA}/2 \pm 12$  mV.

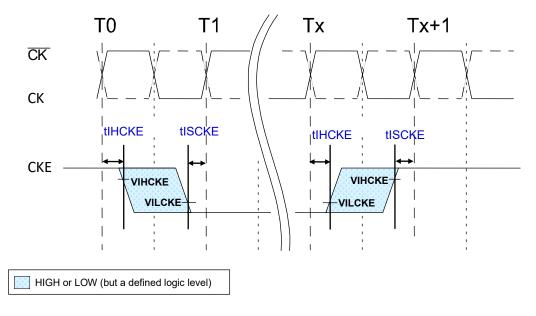

### Single-Ended AC and DC Input Levels for CKE

| Symbol                                          | Parameter                               | Min    | Max                      | Unit | Notes |  |  |  |

|-------------------------------------------------|-----------------------------------------|--------|--------------------------|------|-------|--|--|--|

| $V_{IHCKE}$                                     | V <sub>IHCKE</sub> CKE Input High Level |        | Note 1                   | V    | 1     |  |  |  |

| VILCKE                                          | CKE Input Low Level                     | Note 1 | 0.35 * V <sub>DDCA</sub> | V    | 1     |  |  |  |

| NOTE 1 Overshoot and Undershoot Specifications. |                                         |        |                          |      |       |  |  |  |

### Single-Ended AC and DC Input Levels for DQ and DM

| Comple al                                       | Donomoston                          | 1333/1600                |                          | 1866/                                          | Unit                     | Notes   |         |

|-------------------------------------------------|-------------------------------------|--------------------------|--------------------------|------------------------------------------------|--------------------------|---------|---------|

| Symbol                                          | Parameter                           | Min                      | Max                      | Min                                            | Max                      | Unit    | Notes   |

| $V_{IHDQ}(AC)$                                  | AC input logic high                 | V <sub>Ref</sub> + 0.150 | Note 2                   | V <sub>Ref</sub> + 0.135                       | Note 2                   | V       | 1, 2, 5 |

| $V_{\text{ILDQ}}(AC)$                           | AC input logic low                  | Note 2                   | V <sub>Ref</sub> - 0.150 | Note 2                                         | V <sub>Ref</sub> - 0.135 | V       | 1, 2, 5 |

| $V_{IHDQ}(DC)$                                  | DC input logic high                 | V <sub>Ref</sub> + 0.100 | $V_{	exttt{DDQ}}$        | V <sub>Ref</sub> + 0.100                       | $V_{	extsf{DDQ}}$        | V       | 1       |

| $V_{ILDQ}(DC)$                                  | DC input logic low                  | $V_{SS}$                 | V <sub>Ref</sub> - 0.100 | $V_{\rm SS}$                                   | V <sub>Ref</sub> - 0.100 | V       | 1       |

| $V_{\text{RefDQ}}(\text{DC})$ (DQ ODT disabled) | Reference Voltage for DQ, DM inputs | 0.49 * V <sub>DDQ</sub>  | 0.51 * V <sub>DDQ</sub>  | 0.49 * V <sub>DDQ</sub>                        | 0.51 * V <sub>DDQ</sub>  | V       | 3, 4    |

| $V_{\text{RefDQ}}(\text{DC})$ (DQ ODT enabled)  | Reference Voltage for DQ, DM inputs |                          |                          | V <sub>ODTR</sub> /2 + 0.01 * V <sub>DDQ</sub> | V                        | 3, 5, 6 |         |

NOTE 1 For DQ input only pins.  $V_{Ref} = V_{RefDQ(DC)}$ .

NOTE 2 Overshoot and Undershoot Specifications.

NOTE 3 The ac peak noise on  $V_{\text{RefDQ}}$  may not allow  $V_{\text{RefDQ}}$  to deviate from  $V_{\text{RefDQ(DC)}}$  by more than  $\pm$  1%  $V_{\text{DDQ}}$  (for reference: approx.  $\pm$  12 mV).

NOTE 4 For reference: approx.  $V_{DDQ}/2 \pm 12$  mV.

NOTE 5 For reference: approx.  $V_{ODTR}/2 \pm 12$  mV.

NOTE 6  $R_{ON}$  and  $R_{ODT}$  nominal mode register programmed values are used for the calculation of  $V_{ODTR}$ . For testing purposes a controller RON value of 50  $\Omega$  is used.

$$VODTR = \frac{2RON + RTT}{RON + RTT} \times VDDQ$$

### **VREF** Tolerances

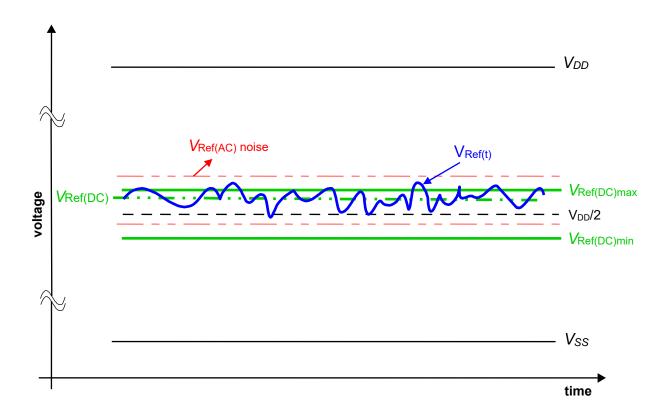

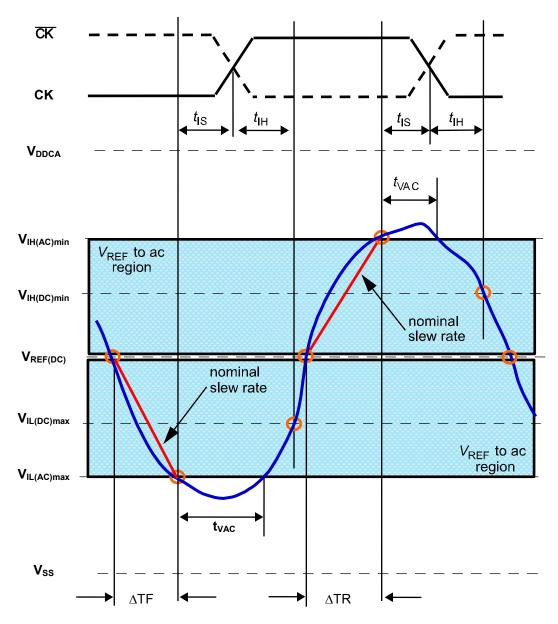

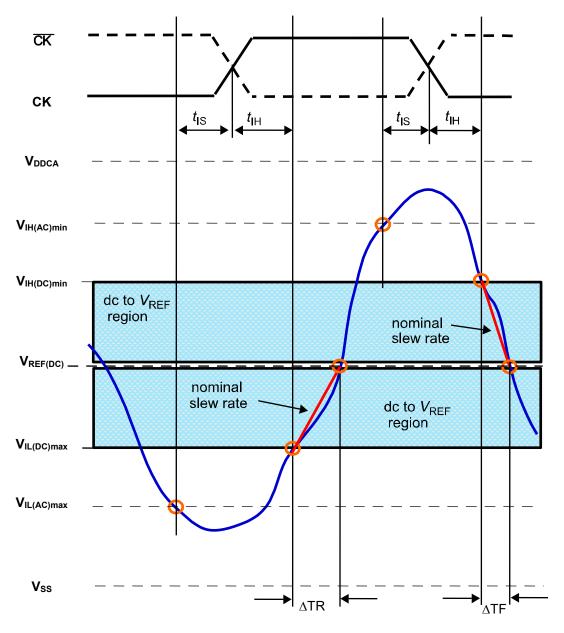

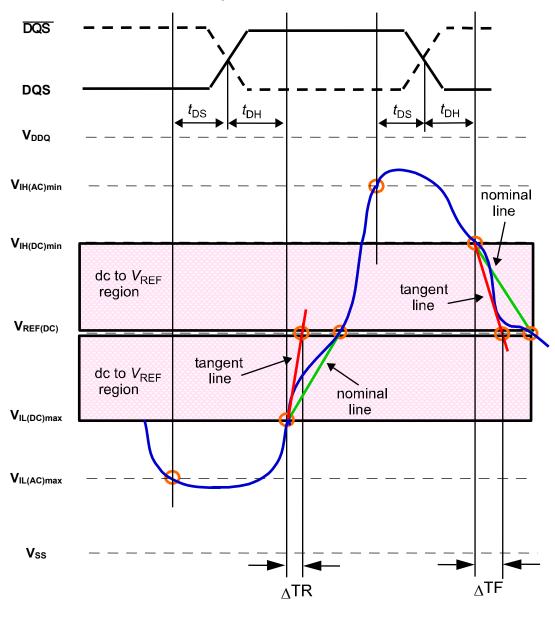

The dc-tolerance limits and ac-noise limits for the reference voltages  $V_{RefCA}$  and  $V_{RefDQ}$  are illustrated below. It shows a valid reference voltage  $V_{Ref}(t)$  as a function of time. ( $V_{Ref}$  stands for  $V_{RefCA}$  and  $V_{RefDQ}$  likewise).  $V_{DD}$  stands for  $V_{DDCA}$  for  $V_{RefCA}$  and  $V_{DDQ}$  for  $V_{RefDQ}$ .  $V_{REF(DC)}$  is the linear average of  $V_{Ref}(t)$  over a very long period of time (e.g. 1 sec) and is specified as a fraction of the linear average of  $V_{DDQ}$  or  $V_{DDCA}$  also over a very long period of time (e.g. 1 sec). This average has to meet the min/max requirements. Furthermore  $V_{Ref}(t)$  may temporarily deviate from  $V_{REF(DC)}$  by no more than  $\pm$  1%  $V_{DD}$ .  $V_{Ref}(t)$  cannot track noise on  $V_{DDQ}$  or  $V_{DDCA}$  if this would send  $V_{Ref}$  outside these specifications.

V<sub>REF</sub> DC Tolerance and V<sub>REF</sub> AC Noise Limits

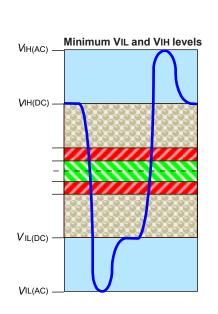

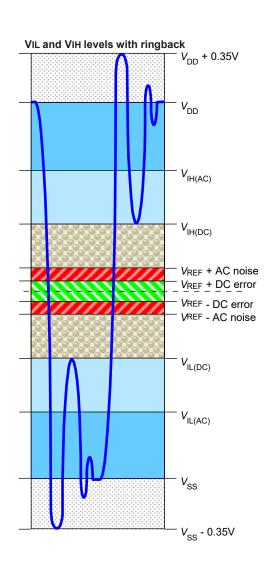

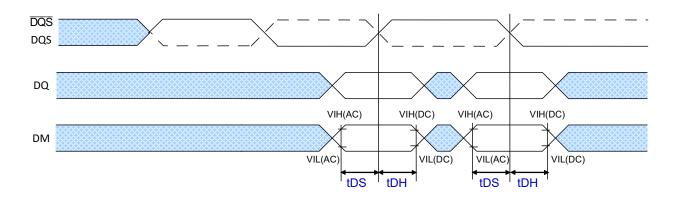

The voltage levels for setup and hold time measurements  $V_{IH(AC)}$ ,  $V_{IH(DC)}$ ,  $V_{IL(AC)}$  and  $V_{IL(DC)}$  are dependent on  $V_{Ref}$ . " $V_{Ref}$  "shall be understood as  $V_{REF(DC)}$  above.

This clarifies that dc-variations of VRef affect the absolute voltage a signal has to reach to achieve a valid high or low level and therefore the time to which setup and hold is measured. System timing and voltage budgets need to account for VREF(DC) deviations from the optimum position within the data-eye of the input signals.

This also clarifies that the LPDDR3 setup/hold specification and derating values need to include time and voltage associated with VRef ac-noise. Timing and voltage effects due to ac-noise on VRef up to the specified limit (+/-1% of VDD) are included in LPDDR3 timings and their associated deratings.

REV 1.0 16 **DLI Memory, Inc.**

# **Input Signal**

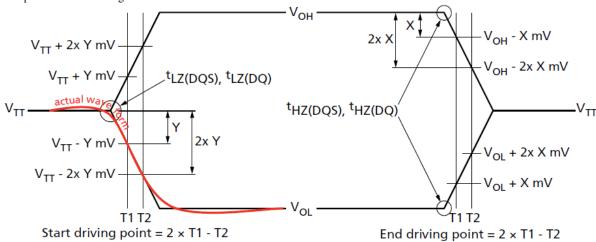

LPDDR3-2133 to LPDDR3-1333 Input Signal

NOTE 1 Numbers reflect typical values.

NOTE 2 For CA[9:0], CK,  $\overline{\text{CK}}$ , and  $\overline{\text{CS}}$ , VDD stands for VDDCA. For DQ, DM, DQS,  $\overline{\text{DQS}}$ , and ODT, VDD stands for VDDQ.

NOTE 3 For CA[9:0], CK,  $\overline{\text{CK}}$ , and  $\overline{\text{CS}}$ , VSS stands for VSS. For DQ, DM, DQS,  $\overline{\text{DQS}}$ , and ODT, VSS stands for VSS.

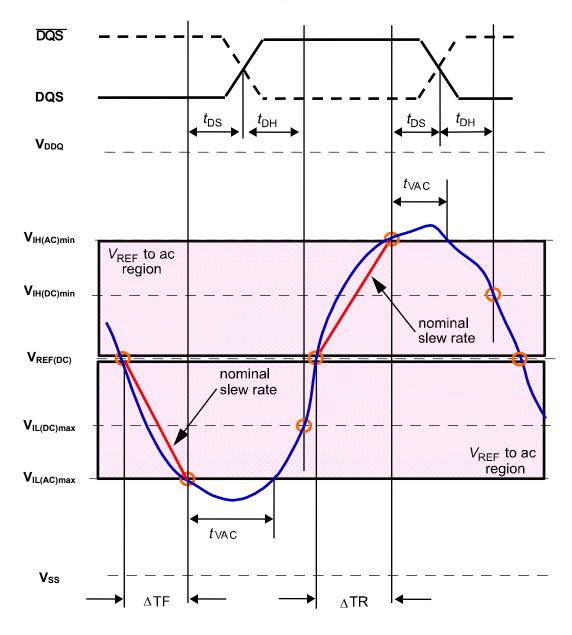

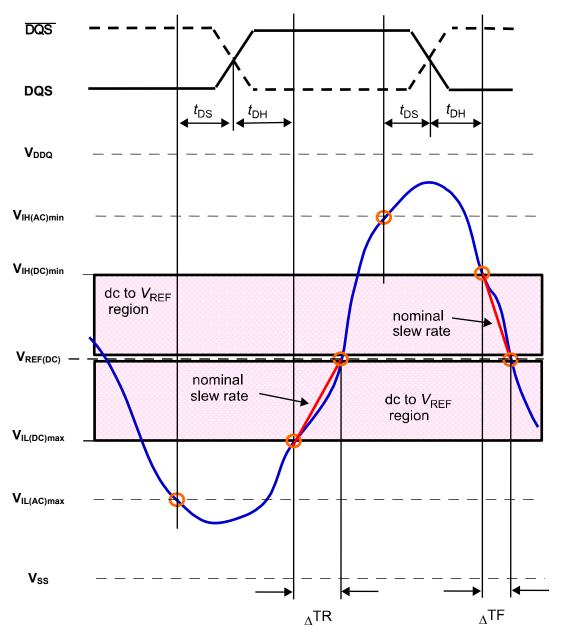

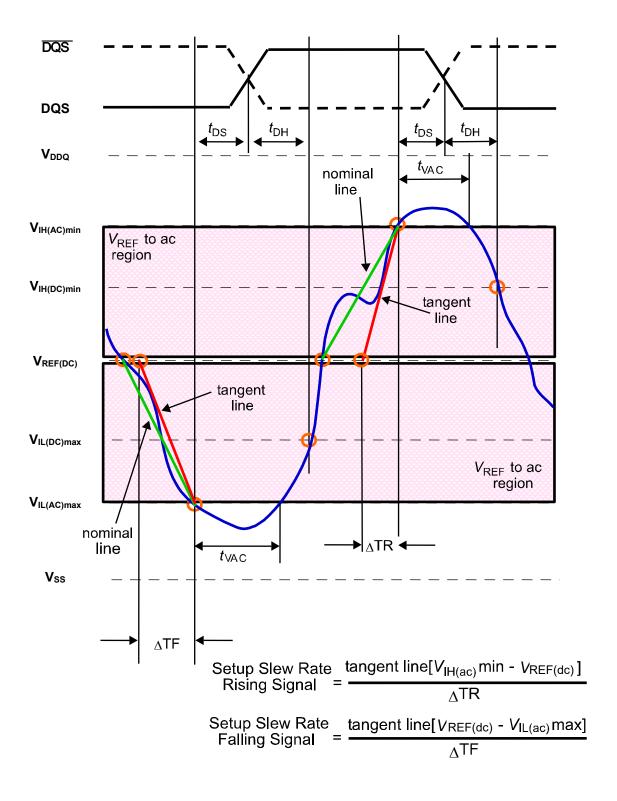

# AC and DC Logic Input Levels for Differential Signals

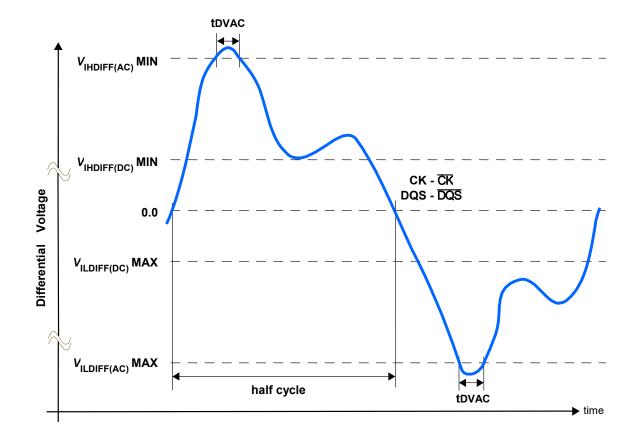

Differential AC Swing Time and "time above ac-level" tDVAC

### Differential swing requirements for clock (CK - CK) and strobe (DQS - DQS)

For CK and  $\overline{CK}$ , VREF = VREFCA(DC); For DQS and  $\overline{DQS}$ , VREF = VREFDQ(DC)

### **Differential AC and DC Input Levels**

| Symbol                  | Parameter                  | Va                                             | Unit                                           | Notes |        |

|-------------------------|----------------------------|------------------------------------------------|------------------------------------------------|-------|--------|

| Бушьог                  | T at affecter              | Min                                            | Max                                            |       | 110103 |

| V <sub>IHdiff(dc)</sub> | Differential input high    | 2 x (V <sub>IH</sub> (dc) - V <sub>Ref</sub> ) | Note 3                                         | V     | 1      |

| V <sub>ILdiff(dc)</sub> | Differential input low     | Note 3                                         | 2 x (V <sub>IL</sub> (dc) - V <sub>Ref</sub> ) | V     | 1      |

| V <sub>IHdiff(ac)</sub> | Differential input high ac | 2 x (V <sub>IH</sub> (ac) - V <sub>Ref</sub> ) | Note 3                                         | V     | 2      |

| $V_{ILdiff(ac)}$        | Differential input low ac  | Note 3                                         | 2 x (V <sub>IL</sub> (ac) - V <sub>Ref</sub> ) | V     | 2      |

- NOTE 1 Used to define a differential signal slew-rate. For CK  $\overline{\text{CK}}$  use  $V_{\text{IH}}/V_{\text{IL(dc)}}$  of CA and  $V_{\text{REFCA}}$ ; for DQS  $\overline{\text{DQS}}$ , use  $V_{\text{IH}}/V_{\text{IL(dc)}}$  of DQs and  $V_{\text{REFDQ}}$ ; if a reduced dc-high or dc-low level is used for a signal group, then the reduced level applies also here.

- NOTE 2 For CK  $\overline{\text{CK}}$  use  $V_{\text{IH}}/V_{\text{IL(ac)}}$  of CA and  $V_{\text{REFCA}}$ ; for DQS  $\overline{\text{DQS}}$ , use  $V_{\text{IH}}/V_{\text{IL(ac)}}$  of DQs and  $V_{\text{REFDQ}}$ ; if a reduced ac-high or ac-low level is used for a signal group, then the reduced level applies also here.

- NOTE 3 These values are not defined, however the single-ended signals CK,  $\overline{\text{CK}}$ , DQS, and  $\overline{\text{DQS}}$  need to be within the respective limits ( $V_{\text{IH}(dc)}$  max,  $V_{\text{IL}(dc)\text{min}}$ ) for single-ended signals as well as the limitations for overshoot and undershoot. Refer to Overshoot and Undershoot Specifications.

- NOTE 4 For CK and  $\overline{CK}$ ,  $V_{Ref} = V_{RefCA(DC)}$ . For DQS and  $\overline{DQS}$ ,  $V_{Ref} = V_{RefDQ(DC)}$ .

### Allowed time before ringback tDVAC for Strobe (DQS - $\overline{DQS}$ )

| Slew Rate [V/ns] |     | c [ps]<br><sub>Ldiff(ac)</sub>   =<br>2133Mbps | @  Vін/і | c [ps]<br>_diff(ac)  =<br>1866Mbps |     | [ps]<br>_ <sub>diff(ac)</sub>   =<br>1600Mbps | t <sub>DVAC</sub> @  V <sub>ІНЛ</sub> 300mV |     |

|------------------|-----|------------------------------------------------|----------|------------------------------------|-----|-----------------------------------------------|---------------------------------------------|-----|

|                  | min | max                                            | min      | min                                | min | max                                           | min                                         | max |

| > 8.0            | 34  | _                                              | 40       | _                                  | 48  | _                                             | 58                                          | _   |

| 8.0              | 34  | _                                              | 40       | _                                  | 48  | _                                             | 58                                          | _   |

| 7.0              | 33  | _                                              | 39       | _                                  | 46  | _                                             | 56                                          | _   |

| 6.0              | 30  | _                                              | 36       | _                                  | 43  | _                                             | 53                                          | _   |

| 5.0              | 27  | _                                              | 33       | _                                  | 40  | _                                             | 50                                          | _   |

| 4.0              | 23  | _                                              | 29       | _                                  | 35  | _                                             | 45                                          | _   |

| 3.0              | 15  | _                                              | 21       | _                                  | 27  | _                                             | 37                                          | _   |

| < 3.0            | 15  | _                                              | 21       | _                                  | 27  | _                                             | 37                                          | _   |

### Allowed time before ringback tDVAC for Clock (CK - $\overline{\text{CK}}$ )

| Slew Rate [V/ns] | $\begin{array}{c cccc} t_{DVAC}  [ps] & t_{DVAC}  [ps] & t_{DVAC}  [ps] \\ \hline @   V_{IH/Ldiff(ac)}  = & @   V_{IH/Ldiff(ac)}  = & & @   V_{IH/Ldiff(ac)}  = \\ \hline 270 \text{mV}  2133 \text{Mbps} & 270 \text{mV}  1866 \text{Mbps} & 300 \text{mV}  1600 \text{Mbps} \end{array}$ |     | $@ V_{\mathrm{IH/Ldiff(ac)}}  =$ |     | $@ V_{\text{IH/Ldiff(ac)}}  =$ |     | t <sub>DVAC</sub> @  V <sub>1H/1</sub> 300mV |     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------|-----|--------------------------------|-----|----------------------------------------------|-----|

| . ,              | min                                                                                                                                                                                                                                                                                        | max | min                              | max | min                            | max | min                                          | max |

| > 8.0            | 34                                                                                                                                                                                                                                                                                         | _   | 40                               | _   | 48                             | -   | 58                                           | _   |

| 8.0              | 34                                                                                                                                                                                                                                                                                         | _   | 40                               | _   | 48                             | _   | 58                                           | _   |

| 7.0              | 33                                                                                                                                                                                                                                                                                         | _   | 39                               | _   | 46                             | _   | 56                                           | _   |

| 6.0              | 30                                                                                                                                                                                                                                                                                         | _   | 36                               | _   | 43                             | _   | 53                                           | _   |

| 5.0              | 27                                                                                                                                                                                                                                                                                         | _   | 33                               | _   | 40                             | _   | 50                                           | _   |

| 4.0              | 23                                                                                                                                                                                                                                                                                         | _   | 29                               | _   | 35                             | -   | 45                                           | -   |

| 3.0              | 15                                                                                                                                                                                                                                                                                         | _   | 21                               | _   | 27                             | -   | 37                                           | 1   |

| < 3.0            | 15                                                                                                                                                                                                                                                                                         | _   | 21                               | _   | 27                             | _   | 37                                           | _   |

### Single-ended requirements for differential signals

Each individual component of a differential signal (CK, DQS,  $\overline{\text{CK}}$ , or  $\overline{\text{DQS}}$ ) has also to comply with certain requirements for single-ended signals. The applicable AC levels for CA and DQ differ by speed bin.

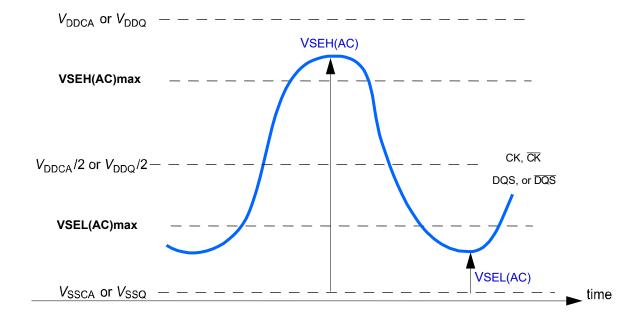

- CK and  $\overline{\text{CK}}$  shall meet VSEH(ac)min / VSEL(ac)max in every half-cycle.

- DQS, DQS shall meet VSEH(ac)min / VSEL(ac)max in every half-cycle preceeding and following a valid transition.

Note that the applicable ac-levels for CA and DQ's are different per speed-bin.

Note that while CA and DQ signal requirements are with respect to Vref, the single-ended components of differential signals have a requirement with respect to  $V_{DDQ}/2$  for DQS,  $\overline{DQS}$  and  $V_{DDCA}/2$  for CK,  $\overline{CK}$ ; this is nominally the same.

The transition of single-ended signals through the ac-levels is used to measure setup time. For single-ended components of differential signals the requirement to reach  $V_{\text{SEL(ac)max}}$ ,  $V_{\text{SEH(ac)min}}$  has no bearing on timing, but adds a restriction on the common mode characteristics of these signals (See tables: Single-Ended AC and DC Input Levels for CA and  $\overline{\text{CS}}$  Inputs; Single-Ended AC and DC Input Levels for DQ and DM).

REV 1.0 21 **DLI Memory, Inc.**

### Single-ended levels for CK, DQS, CK, DQS

| Symbol              | Parameter                                             | Value                           |                                 |      |       |

|---------------------|-------------------------------------------------------|---------------------------------|---------------------------------|------|-------|

| Symbol              | rarameter                                             | Min                             |                                 | Unit | Notes |

| <b>V</b> SEH(AC150) | Single-ended high-level for strobes                   | $(V_{\rm DDQ}/2) + 0.150$       | Note 3                          | V    | 1, 2  |

| V3LII(ACI30)        | Single-ended high-level for CK, CK                    | (V <sub>DDCA</sub> / 2) + 0.150 | Note 3                          | ٧    | 1, 2  |

| <b>V</b> SEL(AC150) | Single-ended low-level for strobes                    | Note 3                          | (V <sub>DDQ</sub> / 2) - 0.150  | ٧    | 1, 2  |

| VSEL(AC130)         | Single-ended low-level for CK, CK                     | Note 3                          | (V <sub>DDCA</sub> / 2) - 0.150 | ٧    | 1, 2  |

| <b>V</b> SEH(AC135) | Single-ended high-level for strobes                   | (V <sub>DDQ</sub> / 2) + 0.135  | Note 3                          | ٧    | 1, 2  |

| VSER(AC155)         | Single-ended high-level for CK, CK                    | $(V_{\rm DDCA} / 2) + 0.135$    | Note 3                          | ٧    | 1, 2  |

| <b>V</b> SEL(AC135) | Single-ended low-level for strobes                    | Note 3                          | (V <sub>DDQ</sub> / 2) - 0.135  | ٧    | 1, 2  |

| V3LL(ACI33)         | Single-ended low-level for CK, $\overline{\text{CK}}$ | Note 3                          | (V <sub>DDCA</sub> / 2) - 0.135 | ٧    | 1, 2  |

- NOTE 1 For CK,  $\overline{\text{CK}}$  use  $V_{\text{SEH}}/V_{\text{SEL(ac)}}$  of CA; for strobes (DQS0,  $\overline{\text{DQS0}}$ , DQS1,  $\overline{\text{DQS1}}$ , DQS2,  $\overline{\text{DQS2}}$ , DQS3,  $\overline{\text{DQS3}}$ ) use  $V_{\text{IH}}/V_{\text{IL(ac)}}$  of DQs.

- NOTE 2  $V_{\rm IH(ac)}/V_{\rm IL(ac)}$  for DQs is based on  $V_{\rm REFDQ}$ ;  $V_{\rm SEH(ac)}/V_{\rm SEL(ac)}$  for CA is based on  $V_{\rm REFCA}$ ; if a reduced ac-high or ac-low level is used for a signal group, then the reduced level applies also here

- NOTE 3 These values are not defined, however the single-ended signals CK,  $\overline{\text{CK}}$ , DQS0,  $\overline{\text{DQS0}}$ , DQS1,  $\overline{\text{DQS1}}$ , DQS2,  $\overline{\text{DQS2}}$ , DQS3,  $\overline{\text{DQS3}}$  need to be within the respective limits ( $V_{\text{IH}(\text{de}) \, \text{max}}$ ,  $V_{\text{IL}(\text{de}) \, \text{min}}$ ) for single-ended signals as well as the limitations for overshoot and undershoot. Refer to Overshoot and Undershoot Specifications.

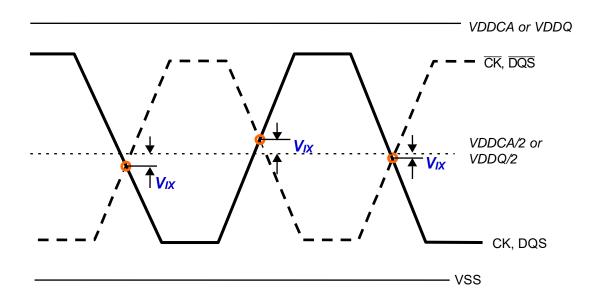

# **Differential Input Cross Point Voltage**

To guarantee tight setup and hold times as well as output skew parameters with respect to clock and strobe, each cross point voltage of differential input signals (CK,  $\overline{CK}$  and DQS,  $\overline{DQS}$ ) must meet the requirements. The differential input cross point voltage  $V_{IX}$  is measured from the actual cross point of true and complement signals to the midlevel between of  $V_{DD}$  and  $V_{SS}$ .

| Crymhol       | Davamatan                                                                           | Valu  | Unit | Notes |       |

|---------------|-------------------------------------------------------------------------------------|-------|------|-------|-------|

| Symbol        | Parameter                                                                           | Min   | Max  | Unit  | Notes |

| <b>V</b> IXCA | Differential Input Cross Point Voltage relative to V <sub>DDCA</sub> /2 for CK, CK  | - 120 | 120  | mV    | 1,2   |

| <b>V</b> IXDQ | Differential Input Cross Point Voltage relative to V <sub>DDQ</sub> /2 for DQS, DQS | - 120 | 120  | mV    | 1,2   |

NOTE 1 The typical value of  $V_{\rm IX(AC)}$  is expected to be about  $0.5 \times V_{\rm DD}$  of the transmitting device, and  $V_{\rm IX(AC)}$  is expected to track variations in  $V_{\rm DD}$ .  $V_{\rm IX(AC)}$  indicates the voltage at which differential input signals must cross.

NOTE 2 For CK and  $\overline{CK}$ ,  $V_{Ref} = V_{RefCA(DC)}$ . For DQS and  $\overline{DQS}$ ,  $V_{Ref} = V_{RefDQ(DC)}$ .

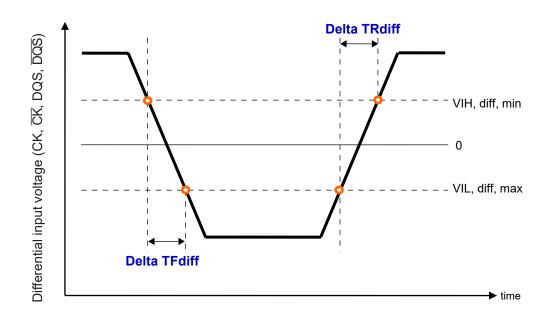

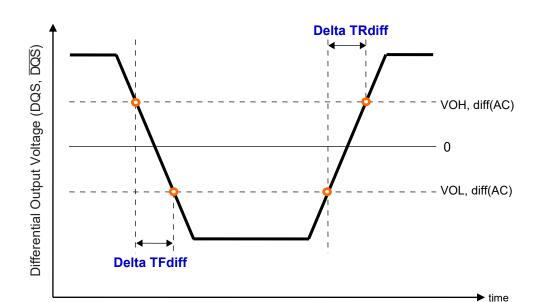

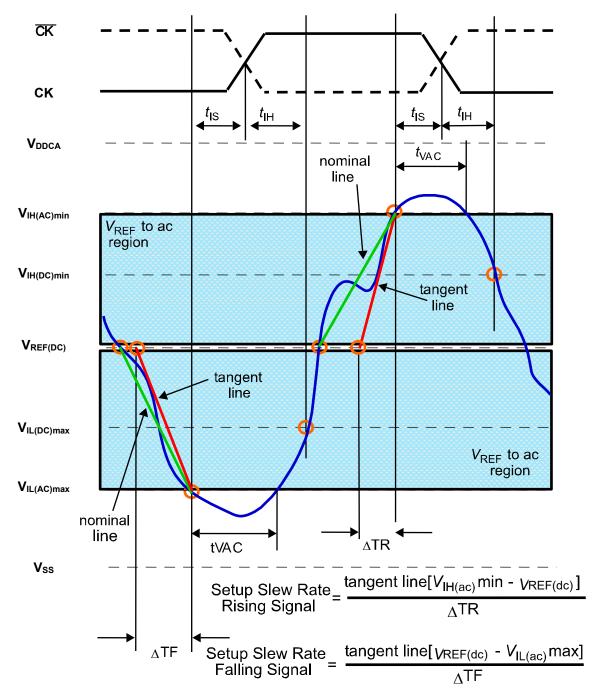

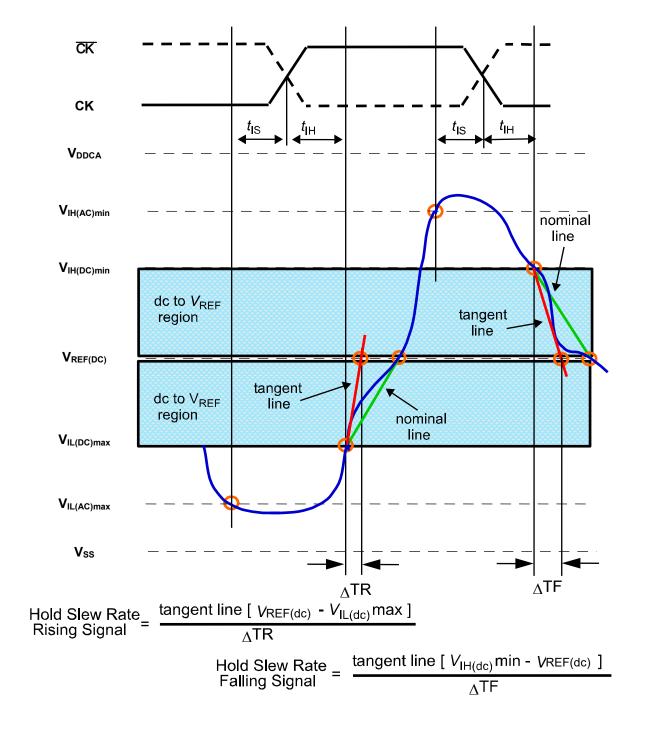

# **Slew Rate Definitions for Differential Input Signals**

### **Differential Input Slew Rate Definition**

| Defined by                                                       |

|------------------------------------------------------------------|

|                                                                  |

| [V <sub>IHdiffmin -</sub> V <sub>ILdiffmax</sub> ] / DeltaTRdiff |

| [V <sub>IHdiffmin</sub> - V <sub>ILdiffmax</sub> ] / DeltaTFdiff |

|                                                                  |

### Differential Input Slew Rate Definition for CK, $\overline{\text{CK}}$ , DQS, and $\overline{\text{DQS}}$

# **AC and DC Output Measurement Levels**

### Single Ended AC and DC Output Levels

| Symbol              | Parameter                                 |                                                                |                                            | Value                         | Unit | Notes |

|---------------------|-------------------------------------------|----------------------------------------------------------------|--------------------------------------------|-------------------------------|------|-------|

| $V_{OH(DC)}$        | DC output high                            | measurement level (for IV curve linearit                       | measurement level (for IV curve linearity) |                               |      | 1     |

| V <sub>OL(DC)</sub> | ODT disabled                              | DC output low measurement level                                |                                            | 0.1 x <i>V</i> <sub>DDQ</sub> | V    | 2     |

| V <sub>OL(DC)</sub> | ODT enabled                               | (for IV curve linearity)                                       | '                                          |                               | V    | 3     |

| V <sub>OH(AC)</sub> | AC output high                            | measurement level (for output slew rate                        | e )                                        | V <sub>REFDQ</sub> + 0.12     | V    |       |

| V <sub>OL(AC)</sub> | AC output low                             | measurement level (for output slew rate                        | )                                          | V <sub>REFDQ</sub> - 0.12     | V    |       |

| ,                   | Output Leakage current (DQ, DM, DQS, DQS) |                                                                | Min                                        | -5                            | uA   |       |

| l <sub>OZ</sub>     | (DQ, DQS, <del>DQS</del>                  | S, $\overline{DQS}$ are disabled; $0V \le V_{OUT} \le V_{DDQ}$ |                                            | 5                             | uA   |       |

NOTE 1  $I_{OH} = -0.1 \text{mA}$ .

NOTE 2  $I_{OL} = 0.1 \text{mA}$ .

NOTE 3 The minimum value is derived when using RTT,min and RON,max (±30% uncalibrated, ±15% calibrated).

### **Differential AC and DC Output Levels**

| Symbol           | Parameter                                                     | Value                     | Unit | Notes |

|------------------|---------------------------------------------------------------|---------------------------|------|-------|

| $V_{OHdiff(AC)}$ | AC differential output high measurement level (for output SR) | + 0.20 x V <sub>DDQ</sub> | V    | 1     |

| $V_{OLdiff(AC)}$ | AC differential output low measurement level (for output SR)  | - 0.20 x V <sub>DDQ</sub> | V    | 2     |

NOTE 1  $I_{OH} = -0.1 \text{mA}$ .

NOTE 2  $I_{OL} = 0.1 \text{mA}$

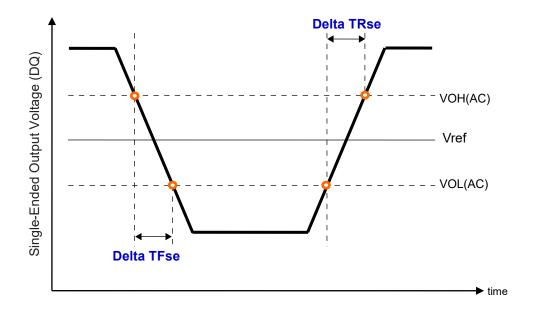

### **Single Ended Output Slew Rate**

With the reference load for timing measurements, output slew rate for falling and rising edges is defined and measured between  $V_{\text{OL(AC)}}$  and  $V_{\text{OH(AC)}}$  for single ended signals.

### Single-ended Output Slew Rate Definition

| Description                                                                   | Meas                | ured                | D.C., J.L.                                               |  |  |  |  |

|-------------------------------------------------------------------------------|---------------------|---------------------|----------------------------------------------------------|--|--|--|--|

| Description                                                                   | from                | to                  | Defined by                                               |  |  |  |  |

| Single-ended output slew rate for rising edge                                 | $V_{	ext{OL(AC)}}$  | V <sub>OH(AC)</sub> | [V <sub>OH(AC)</sub> - V <sub>OL(AC)</sub> ] / DeltaTRse |  |  |  |  |

| Single-ended output slew rate for falling edge                                | V <sub>OH(AC)</sub> | V <sub>OL(AC)</sub> | [V <sub>OH(AC)</sub> - V <sub>OL(AC)</sub> ] / DeltaTFse |  |  |  |  |

| NOTE Output slew rate is verified, and may not be subject to production test. |                     |                     |                                                          |  |  |  |  |

### Single-ended Output Slew Rate

| Domenton                                                     | Ck al  | Va               | TI:4             |       |

|--------------------------------------------------------------|--------|------------------|------------------|-------|

| Parameter                                                    | Symbol | Min <sup>1</sup> | Max <sup>2</sup> | Units |

| Single-ended Output Slew Rate (RON = $40\Omega$ +/- $30\%$ ) | SRQse  | 1.5              | 4.0              | V/ns  |

| Output slew-rate matching Ratio (Pull-up to Pull-down)       |        | 0.7              | 1.4              |       |

Description: SR: Slew Rate; Q: Query Output (like in DQ, which stands for Data-in, Query-Output); se: Single-ended Signals

- NOTE 1 Measured with output reference load.

- NOTE 2 The ratio of pull-up to pull-down slew rate is specified for the same temperature and voltage, over the entire temperature and voltage range. For a given output, it represents the maximum difference between pull-up and pull-down drivers due to process variation.

- NOTE 3 The output slew rate for falling and rising edges is defined and measured between  $V_{OL(AC)}$  and  $V_{OH(AC)}$ .

- NOTE 4 Slew rates are measured under average SSO conditions, with 50% of DQ signals per data byte switching.

### **Differential Output Slew Rate**

With the reference load for timing measurements, output slew rate for falling and rising edges is defined and measured between VOLdiff(AC) and VOHdiff(AC) for differential signals.

### **Differential Output Slew Rate Definition**

| Description                                                                     | Meas                    | ured                   | Defined by                                                         |  |  |  |

|---------------------------------------------------------------------------------|-------------------------|------------------------|--------------------------------------------------------------------|--|--|--|

| Description                                                                     | from to                 |                        | Defined by                                                         |  |  |  |

| Differential output slew rate for rising edge                                   | $V_{OLdiff(AC)}$        | $V_{OHdiff(AC)}$       | $[V_{OHdiff(AC)} - V_{OLdiff(AC)}]$ / $DeltaTRdiff$                |  |  |  |

| Differential output slew rate for falling edge                                  | V <sub>OHdiff(AC)</sub> | $V_{	ext{OLdiff(AC)}}$ | [V <sub>OHdiff(AC)</sub> - V <sub>OLdiff(AC)</sub> ] / DeltaTFdiff |  |  |  |

| NOTE 1 Output slew rate is verified, and may not be subject to production test. |                         |                        |                                                                    |  |  |  |

### **Differential Output Slew Rate**

| Parameter                                                      | Symbol  | Va  | Unite |       |

|----------------------------------------------------------------|---------|-----|-------|-------|

| rarameter                                                      | Symbol  | Min | Max   | Units |

| Differential Output Slew Rate ( $R_{ON} = 40\Omega + /-30\%$ ) | SRQdiff | 3.0 | 8.0   | V/ns  |

Description: SR: Slew Rate; Q: Query Output (like in DQ, which stands for Data-in, Query-Output); diff: Differential Signals

NOTE 1 Measured with output reference load.

NOTE 2 The output slew rate for falling and rising edges is defined and measured between  $V_{OL(AC)}$  and  $V_{OH(AC)}$ .

NOTE 3 Slew rates are measured under normal SSO conditions, with 50% of DQ signals per data byte switching.

REV 1.0 28 **DLI Memory, Inc.**

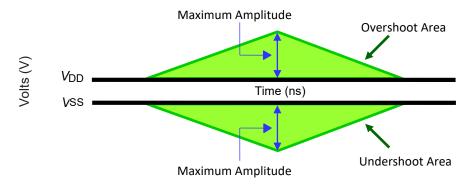

### **Overshoot and Undershoot Specifications**

### AC Overshoot/Undershoot Specification

| Parameter                                           | 1333 | 1600/1866/2133 | Units |      |

|-----------------------------------------------------|------|----------------|-------|------|

| Maximum peak amplitude allowed for overshoot area.  | Max  |                | V     |      |

| Maximum peak amplitude allowed for undershoot area. | Max  |                | V     |      |

| Maximum area above VDD.                             | Max  | 0.12           | V-ns  |      |

| Maximum area below VSS.                             | Max  | 0.12           | 0.10  | V-ns |

- NOTE 1  $V_{DD}$  stands for  $V_{DDCA}$  for CA[9:0], CK,  $\overline{CK}$ ,  $\overline{CS}$ , and CKE.  $V_{DD}$  stands for  $V_{DDQ}$  for DQ, DM, ODT, DQS, and  $\overline{DQS}$ .

- NOTE 2 Vss stands for Vss for CA[9:0], CK, CK, CS, and CKE. Vss stands for Vss for DQ, DM, ODT, DQS, and DQS.

- NOTE 3 Maximum peak amplitude values are referenced from actual VDD and Vss values.

- NOTE 4 Maximum area values are referenced from maximm operating VDD and Vss values.

### **Overshoot and Undershoot Definition**

- NOTE 1 VDD = VDDCA for CA[9:0], CK,  $\overline{CK}$ ,  $\overline{CS}$ , and CKE. VDD = VDDQ for DQ, DM, DQS,  $\overline{DQS}$ , and ODT.

- NOTE 2 VSS = VSS for CA[9:0], CK,  $\overline{CK}$ ,  $\overline{CS}$ , and CKE. VSS = VSS for DQ, DM, DQS,  $\overline{DQS}$ , and ODT.

- NOTE 3 Absolute maximum requirements apply.

- NOTE 4 Maximum peak amplitude values are referenced from actual VDD and Vss values.

- NOTE 5 Maximum area values are referenced from maximum operating VDD and Vss values.

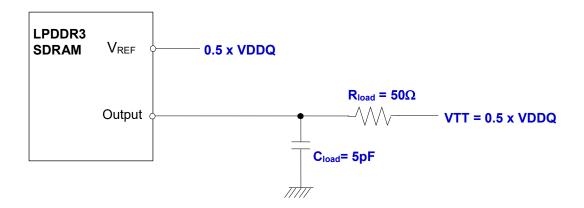

# **Output buffer characteristics**

### **HSUL\_12 Driver Output Timing Reference Load**

These 'Timing Reference Loads' are not intended as a precise representation of any particular system environment or a depiction of the actual load presented by a production tester. System designers should use IBIS or other simulation tools to correlate the timing reference load to a system environment. Manufacturers correlate to their production test conditions, generally one or more coaxial transmission lines terminated at the tester electronics.

NOTE 1 All output timing parameter values (tDQSCK, tDQSQ, tHZ, tRPRE, etc.) are reported with respect to this reference load. This reference load is also used to report slew rate.

REV 1.0 30 *DLI Memory, Inc.*

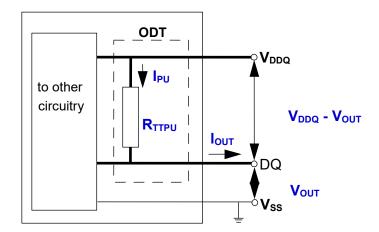

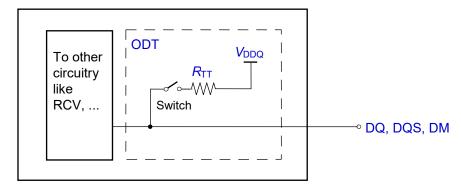

### **ODT Levels and I-V Characteristics**

On-Die Termination effective resistance,  $R_{TT}$ , is defined by mode register MR11[1:0]. ODT is applied to the DQ, DM, and DQS/ $\overline{DQS}$  pins. A functional representation of the on-die termination is shown in the figure below.

$R_{\rm TT}$  is defined by the following formula:

$$R_{\text{TTPU}} = (V_{\text{DDQ}} - V_{\text{Out}}) / |I_{\text{Out}}|$$

REV 1.0 31 *DLI Memory, Inc.*

### Input/output capacitance

| Parameter                                          | Symbol             | Min   | Max  | Units | Notes   |

|----------------------------------------------------|--------------------|-------|------|-------|---------|

| Input capacitance, CK and CK                       | Сск                | 0.5   | 1.4  | pF    | 1,2     |

| Input capacitance delta, CK and CK                 | $C_{DCK}$          | 0     | 0.15 | pF    | 1,2,3   |

| Input capacitance, all other input-only pins       | Cı                 | 0.5   | 1.4  | pF    | 1,2,4   |

| Input capacitance delta, all other input-only pins | C <sub>DI</sub>    | -0.20 | 0.20 | pF    | 1,2,5   |

| Input/output capacitance, DQ, DM, DQS, DQS         | C <sub>IO</sub>    | 1.0   | 2.0  | pF    | 1,2,6,7 |

| Input/output capacitance delta, DQS, DQS           | $C_{	extsf{DDQS}}$ | 0     | 0.2  | pF    | 1,2,7,8 |

| Input/output capacitance delta, DQ, DM             | C <sub>DIO</sub>   | -0.25 | 0.25 | pF    | 1,2,7,9 |

| Input/output capacitance ZQ Pin                    | $C_{ZQ}$           | 0     | 2.65 | pF    | 1,2     |

$(T_{\text{OPER}}; V_{\text{DDQ}} = 1.14 - 1.3 \text{V}; V_{\text{DDCA}} = 1.14 - 1.3 \text{V}; V_{\text{DD1}} = 1.7 - 1.95 \text{V}, V_{\text{DD2}} = 1.14 - 1.3 \text{V})$

- NOTE 1 This parameter applies to die devices, RDL if needed (does not include package capacitance).

- NOTE 2 This parameter is not subject to production test. It is verified. The capacitance is measured according to JEP147 (Procedure for measuring input capacitance using a vector network analyzer (VNA) with V<sub>DD1</sub>, V<sub>DD2</sub>, V<sub>DDQ</sub>, V<sub>SS</sub>, V<sub>SS</sub>, V<sub>SS</sub> applied and all other pins floating.

- NOTE 3 Absolute value of  $C_{CK}$   $C_{\overline{CK}}$ .

- NOTE 4  $C_{\rm I}$  applies to  $\overline{\text{CS}}$ , CKE, CA0-CA9, ODT.

- NOTE 5  $C_{DI} = C_{I} 0.5 * (C_{CK} + C_{\overline{CK}})$

- NOTE 6 DM loading matches DQ and DQS.

- NOTE 7 MR3 I/O configuration DS OP3-OP0 = 0001B (34.3  $\Omega$  typical)

- NOTE 8 Absolute value of  $C_{DQS}$  and  $C_{\overline{DQS}}$ .

- NOTE 9  $C_{DIO} = C_{IO} 0.5 * (C_{DQS} + C_{\overline{DQS}})$  in byte-lane.

# **IDD Specification Parameters and Test Conditions**

### **IDD Measurement Conditions**

The following definitions are used within the  $I_{DD}$  measurement tables unless stated otherwise:

LOW:  $VIN \leq VIL(DC) MAX$ HIGH:  $VIN \geq VIH(DC) MIN$

STABLE: Inputs are stable at a HIGH or LOW level

SWITCHING: See following 3 tables.

### **Definition of Switching for CA Input Signals**

|           |                                     |                                     | Sv                                  | witching for CA                     | A                                   |                                     |                                     |                                     |

|-----------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

|           | CK<br>(RISING) /<br>CK<br>(FALLING) | CK<br>(FALLING) /<br>CK<br>(RISING) |

| Cycle     | 1                                   | N                                   | N-                                  | +1                                  | N-                                  | +2                                  | N-                                  | +3                                  |

| <u>CS</u> | HIGH                                |                                     | HIG                                 | HIGH                                |                                     | GH                                  | HI                                  | GH                                  |

| CA0       | HIGH                                | LOW                                 | LOW                                 | LOW                                 | LOW                                 | HIGH                                | HIGH                                | HIGH                                |

| CA1       | HIGH                                | HIGH                                | HIGH                                | LOW                                 | LOW                                 | LOW                                 | LOW                                 | HIGH                                |

| CA2       | HIGH                                | LOW                                 | LOW                                 | LOW                                 | LOW                                 | HIGH                                | HIGH                                | HIGH                                |

| CA3       | HIGH                                | HIGH                                | HIGH                                | LOW                                 | LOW                                 | LOW                                 | LOW                                 | HIGH                                |

| CA4       | HIGH                                | LOW                                 | LOW                                 | LOW                                 | LOW                                 | HIGH                                | HIGH                                | HIGH                                |

| CA5       | HIGH                                | HIGH                                | HIGH                                | LOW                                 | LOW                                 | LOW                                 | LOW                                 | HIGH                                |

| CA6       | HIGH                                | LOW                                 | LOW                                 | LOW                                 | LOW                                 | HIGH                                | HIGH                                | HIGH                                |

| CA7       | HIGH                                | HIGH                                | HIGH                                | LOW                                 | LOW                                 | LOW                                 | LOW                                 | HIGH                                |

| CA8       | HIGH                                | LOW                                 | LOW                                 | LOW                                 | LOW                                 | HIGH                                | HIGH                                | HIGH                                |

| CA9       | HIGH                                | HIGH                                | HIGH                                | LOW                                 | LOW                                 | LOW                                 | LOW                                 | HIGH                                |

NOTE 2  $\,$  50% of CA bus is changing between HIGH and LOW once per clock for the CA bus.

NOTE 3 The above pattern (N, N+1, N+2, N+3...) is used continuously during  $I_{DD}$  measurement for  $I_{DD}$  values that require SWITCHING on the CA bus.

**Definition of Switching for IDD4R**

| Clock   | CKE | CS | Clock Cycle<br>Number | Command      | CA[0:2] | CA[3:9] | All DQ |

|---------|-----|----|-----------------------|--------------|---------|---------|--------|

| Rising  | Н   | L  | N                     | Read_Rising  | HLH     | LHLHLHL | L      |

| Falling | Н   | L  | N                     | Read_Falling | LLL     | LLLLLLL | L      |

| Rising  | Н   | Н  | N + 1                 | NOP          | LLL     | LLLLLLL | Н      |

| Falling | Н   | Н  | N + 1                 | NOP          | LLL     | LLLLLLL | L      |

| Rising  | Н   | Н  | N + 2                 | NOP          | LLL     | LLLLLLL | Н      |

| Falling | Н   | Н  | N + 2                 | NOP          | LLL     | LLLLLLL | Н      |

| Rising  | Н   | Н  | N + 3                 | NOP          | LLL     | LLLLLLL | Н      |

| Falling | Н   | Н  | N + 3                 | NOP          | HLH     | HLHLLHL | L      |

| Rising  | Н   | L  | N + 4                 | Read_Rising  | HLH     | HLHLLHL | Н      |

| Falling | Н   | L  | N + 4                 | Read_Falling | LHH     | нннннн  | Н      |

| Rising  | Н   | Н  | N + 5                 | NOP          | ННН     | НННННН  | Н      |

| Falling | Н   | Н  | N + 5                 | NOP          | ННН     | НННННН  | L      |

| Rising  | Н   | Н  | N + 6                 | NOP          | ННН     | нннннн  | L      |

| Falling | Н   | Н  | N + 6                 | NOP          | ННН     | нннннн  | L      |

| Rising  | Н   | Н  | N + 7                 | NOP          | ННН     | нннннн  | Н      |

| Falling | Н   | Н  | N + 7                 | NOP          | HLH     | LHLHLHL | L      |

NOTE 1 Data strobe (DQS) is changing between HIGH and LOW every clock cycle.

NOTE 2 The above pattern (N, N+1...) is used continuously during  $I_{\rm DD}$  measurement for  $I_{\rm DD4R}$ .

**Definition of Switching for IDD4W**

| Clock   | СКЕ | <del>cs</del> | Clock Cycle Number | Command       | CA[0:2] | CA[3:9] | All DQ |

|---------|-----|---------------|--------------------|---------------|---------|---------|--------|

| Rising  | Н   | L             | N                  | Write_Rising  | HLL     | LHLHLHL | L      |

| Falling | Н   | L             | N                  | Write_Falling | LLL     | LLLLLLL | L      |

| Rising  | Н   | Н             | N + 1              | NOP           | LLL     | LLLLLLL | Н      |

| Falling | Н   | Н             | N + 1              | NOP           | LLL     | LLLLLLL | L      |

| Rising  | Н   | Н             | N + 2              | NOP           | LLL     | LLLLLLL | Н      |

| Falling | Н   | Н             | N + 2              | NOP           | LLL     | LLLLLLL | Н      |

| Rising  | Н   | Н             | N + 3              | NOP           | LLL     | LLLLLLL | Н      |

| Falling | Н   | Н             | N + 3              | NOP           | HLL     | HLHLLHL | L      |

| Rising  | Н   | L             | N + 4              | Write_Rising  | HLL     | HLHLLHL | Н      |

| Falling | Н   | L             | N + 4              | Write_Falling | LHH     | нннннн  | Н      |

| Rising  | Н   | Н             | N + 5              | NOP           | ННН     | нннннн  | Н      |

| Falling | Н   | Н             | N + 5              | NOP           | ННН     | нннннн  | L      |

| Rising  | Н   | Н             | N + 6              | NOP           | ННН     | нннннн  | L      |

| Falling | Н   | Н             | N + 6              | NOP           | ННН     | нининин | L      |

| Rising  | Н   | Н             | N + 7              | NOP           | ННН     | нннннн  | Н      |

| Falling | Н   | Н             | N + 7              | NOP           | HLL     | LHLHLHL | L      |

NOTE 1 Data strobe (DQS) is changing between HIGH and LOW every clock cycle.

NOTE 2 Data masking (DM) must always be driven LOW.

NOTE 3 The above pattern (N, N+1...) is used continuously during  $I_{DD}$  measurement for  $I_{DD4W}$ .

# **IDD Specifications**

$I_{\rm DD}$  values are for the entire operating voltage range, and all of them are for the entire standard range.

### $\emph{I}_{\text{DD}}$ Specification Parameters and Operating Conditions

Notes 1, 2, 3 apply for all values.

| Parameter/Condition                                                                                                                            | Symbol               | Power Supply              | Notes |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------|-------|

| Operating one bank active-precharge current:                                                                                                   | $I_{ m DD01}$        | $V_{ m DD1}$              |       |

| tCK =tCK (MIN); tRC = tRC (MIN); CKE is HIGH; $\overline{CS}$ is HIGH between valid commands; CA bus inputs are switching; Data bus inputs are | $I_{ m DD02}$        | $V_{ m DD2}$              |       |

| stable; ODT is disabled                                                                                                                        | $I_{ m DD0in}$       | $V_{ m DDCA},V_{ m DDQ}$  | 4     |

| Idle power-down standby current:                                                                                                               | $I_{ m DD2P1}$       | $V_{ m DD1}$              |       |

| tCK = tCK (MIN); CKE is LOW; $\overline{\text{CS}}$ is HIGH; All banks are idle; CA bus                                                        | $I_{ m DD2P2}$       | $V_{ m DD2}$              |       |

| inputs are switching; Data bus inputs are stable; ODT is disabled                                                                              | $I_{ m DD2P,in}$     | $V_{ m DDCA},V_{ m DDQ}$  | 4     |

| Idle power-down standby current with clock stop:                                                                                               | $I_{ m DD2PS1}$      | $V_{ m DD1}$              |       |

| CK= LOW, $\overline{\text{CK}}$ = HIGH; CKE is LOW; $\overline{\text{CS}}$ is HIGH; All banks are                                              | $I_{ m DD2PS2}$      | $V_{ m DD2}$              |       |

| idle; CA bus inputs are stable; Data bus inputs are stable; ODT is disabled                                                                    | $I_{ m DD2PS,in}$    | $V_{ m DDCA},V_{ m DDQ}$  | 4     |

| Idle non-power-down standby current:                                                                                                           | $I_{\mathrm{DD2N1}}$ | $V_{ m DD1}$              |       |

| tCK = tCK (MIN); CKE is HIGH; $\overline{\text{CS}}$ is HIGH; All banks are idle; CA bus                                                       | $I_{ m DD2N2}$       | $V_{ m DD2}$              |       |

| inputs are switching; Data bus inputs are stable; ODT is disabled                                                                              | $I_{ m DD2N,in}$     | $V_{ m DDCA},V_{ m DDQ}$  | 4     |

| Idle non-power-down standby current with clock stopped:                                                                                        | $I_{ m DD2NS1}$      | $V_{ m DD1}$              |       |

| CK = LOW; $\overline{\text{CK}}$ = HIGH; CKE is HIGH; $\overline{\text{CS}}$ is HIGH;                                                          | $I_{ m DD2NS2}$      | $V_{ m DD2}$              |       |

| All banks are idle; CA bus inputs are stable; Data bus inputs are stable; ODT is disabled                                                      | $I_{ m DD2NS.in}$    | $V_{ m DDCA}, V_{ m DDQ}$ | 4     |

| Active power-down standby current:                                                                                                             | $I_{\mathrm{DD3P1}}$ | $V_{ m DD1}$              | -     |

| tCK = tCK (MIN); CKE is LOW; $\overline{\text{CS}}$ is HIGH; One bank is active; CA bus                                                        | $I_{\mathrm{DD3P2}}$ | $V_{ m DD2}$              |       |

| inputs are switching; Data bus inputs are stable; ODT is disabled                                                                              | $I_{ m DD3P,in}$     | $V_{ m DDCA}, V_{ m DDQ}$ | 4     |

| Active power-down standby current with clock stop:                                                                                             | $I_{ m DD3PS1}$      | $V_{ m DD1}$              |       |

| CK = LOW, $\overline{\text{CK}}$ = HIGH; CKE is LOW; $\overline{\text{CS}}$ is HIGH; One bank is active;                                       | $I_{ m DD3PS2}$      | $V_{ m DD2}$              |       |

| CA bus inputs are stable; Data bus inputs are stable; ODT is disabled                                                                          | $I_{ m DD3PS,in}$    | $V_{ m DDCA},V_{ m DDQ}$  | 4     |

| Active non-power-down standby current:                                                                                                         | $I_{ m DD3N1}$       | $V_{ m DD1}$              |       |

| tCK = tCK (MIN); CKE is HIGH; $\overline{\text{CS}}$ is HIGH; One bank is active; CA bus                                                       | $I_{ m DD3N2}$       | $V_{ m DD2}$              |       |

| inputs are switching; Data bus inputs are stable; ODT is disabled                                                                              | $I_{ m DD3N,in}$     | $V_{ m DDCA},V_{ m DDQ}$  | 4     |

| Active non-power-down standby current with clock stopped:                                                                                      | $I_{ m DD3NS1}$      | $V_{ m DD1}$              |       |